利用Cadence设计COMS低噪声放大器

时间:06-11

来源:EDN

点击:

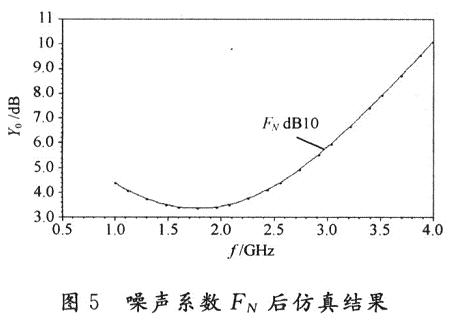

与电路的前仿结果相比,后仿真的噪声系数有一定的上升,这说明电路中的寄生参数会使电路的噪声性能恶化。

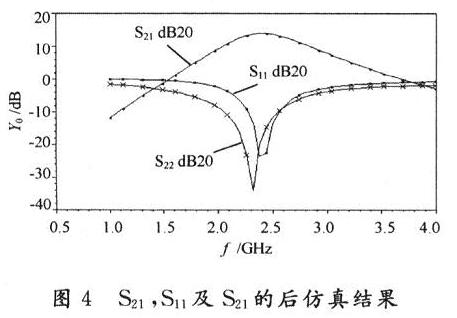

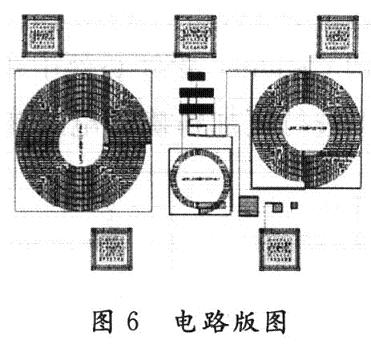

图4、图5是完成版图之后,考虑寄生参数的电路后仿真结果。图4是S参数的后仿真结果。由S11,S22的曲线可知,在2.4 GHz的中心频率附近,S11,S22<-10 dB。可见,输入、输出电路均有比较好的匹配。图5是噪声系数FN的后仿真结果。图6为电路版图。

3 结 语

结合一个具体的低噪声放大器(LNA)设计实例,采用CHRT的0.35μm RFCMOS工艺,在EDA软件IC 5.1设计环境中设计了一个2.4 GHz的低噪声放大器。设计过程中完成了电路原理图仿真、版图设计以及后仿真。实验结果表明该低噪声放大器具有较好的电路性能。结合设计过程,还介绍了如何运用Cadence软件对CMOS低噪声放大器进行电路设计和仿真。

- 利用阻性负载增强LNA稳定性(中)(11-19)

- 稳定低噪声放大器中晶体管工作点的设计方法(下)(11-20)

- 利用阻性负载增强LNA稳定性(下)(11-19)

- 稳定低噪声放大器中晶体管工作点的设计方法(上)(11-19)

- 利用阻性负载增强LNA稳定性(上)(11-19)

- 使用前置放大器有助于提高测量质量(01-16)