LED全彩屏数字视频信号处理电路的设计

时间:04-19

来源:现代电子技术

点击:

1 引 言

LED视频显示屏由于亮度高、视角广、寿命长、性价比高,而且具有可与计算机同步显示各种文字、图形、图像,可实时播放电视、录像、影碟等视频信号,可即时输入、编辑各种多媒体数据等优点,使其在街头、广场、商业中心、运动场所、娱乐场所、控制中心许多公共场合得到了广泛的应用。但是由于技术的问题,特大视频显示屏还面临着严峻的挑战,主要表现在灰度级低,亮度损失严重,刷新速度低。另外,本文的视频信号源来自DVI(Digital Video Interface)接口,DVI接口输出的为数字视频信号,信息量大,一般是先经过外部RAM(Random Array Memory)缓存,然后由处理器对视频信号进行处理。可用于数字图像存储的外部存储器有很多种,如SRAM,DRAM和SDRAM,它们的容量和速度各不相同。DRAM和SDRAM属于动态存储器,容量大,使用中需要刷新,当处理器没有外部动态RAM接口时,就需要设计刷新电路,这给系统应用带来不便;SRAM不用刷新,不需要专用接口,实时性好,并且可以进行跳地址寻址,所以本文利用SRAM作为外部缓存存储器。采用分场分区存储技术,使刷新频率大为提高,图像显示效果清晰稳定,实现了分辨率800×256,刷新频率90 Hz,红绿蓝三色256×256×256灰度级的视频显示系统。同时,采用该技术,亮度和灰度级方便可调,亮度损失小。

2 系统组成

LED视频显示系统总体框图如图1所示:该系统由发送和接收两部分组成,发送部分的功能主要是对DVI接口传输的视频信号进行编解码形成24 b真彩色视频数据和点时钟(CLK),行同步信号(HS),场同步信号(VS),数据有效信号(DE)等控制信号,通过LVDS(Low Voltage Differential Signaling)电平传输到接收卡上,经过接收卡的数据处理传送给具有特定驱动结构(1/8扫描方式,74HC595驱动芯片)韵LED大屏。本文的重点是介绍接收卡的数据处理模块。

数据处理流程如图2所示:接收卡接收发送卡传输过来的视频信号(控制信号和数据信号),将视频信号中的数据经过位面分离,分场存入外部缓存,然后分区读出,传送给显示驱动屏。其中位面分离模块将不同数据的同权位重新组合成新的数据存储在存储器中。外部缓存采用两个SRAM乒乓缓存的技术,实现数据的流水线处理。下面分别介绍位面分离模块和分场分区存储的原理和实现。

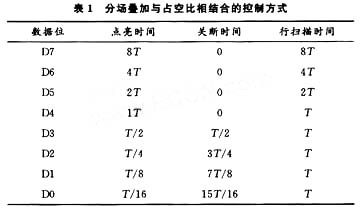

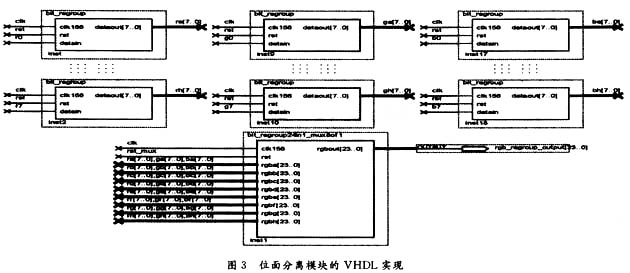

视频显示屏采用的灰度级控制方式为分场叠加与占空比相结合的方式,如表1所示:其中分场叠加是指用不同场次的恒频扫描来实现不同灰度级,如表1的D7~D4;占空比控制是指控制点亮时间与关断时间的占空比来实现灰度的调节,如表1的D3~D0。而这两种方式的前提都是要实现视频数据的位面分离。位面分离用FPGA来实现,一共包括两大模块,数据移位寄存器和数据选择器。用VHDL实现的原理框图如图3所示,其中r0-7,g0-7,b0-7分别是真彩色图像数据的红绿蓝三色,分别占用一个字节。把这24位数据线分别通过一个8位宽数据移位寄存器寄存,然后通过一个颜色位选择器输出到外部缓存器中。通过控制缓存器的地址实现位面分离,外部缓存的数据宽度为24位,使RGB三种颜色并行进行位面分离。其中移位寄存器使用了流水线的技术,在锁存输出前8个数据的同权位的同时,移进第9个数据的同权位,这样提高了数据处理的效率。

LED视频显示屏由于亮度高、视角广、寿命长、性价比高,而且具有可与计算机同步显示各种文字、图形、图像,可实时播放电视、录像、影碟等视频信号,可即时输入、编辑各种多媒体数据等优点,使其在街头、广场、商业中心、运动场所、娱乐场所、控制中心许多公共场合得到了广泛的应用。但是由于技术的问题,特大视频显示屏还面临着严峻的挑战,主要表现在灰度级低,亮度损失严重,刷新速度低。另外,本文的视频信号源来自DVI(Digital Video Interface)接口,DVI接口输出的为数字视频信号,信息量大,一般是先经过外部RAM(Random Array Memory)缓存,然后由处理器对视频信号进行处理。可用于数字图像存储的外部存储器有很多种,如SRAM,DRAM和SDRAM,它们的容量和速度各不相同。DRAM和SDRAM属于动态存储器,容量大,使用中需要刷新,当处理器没有外部动态RAM接口时,就需要设计刷新电路,这给系统应用带来不便;SRAM不用刷新,不需要专用接口,实时性好,并且可以进行跳地址寻址,所以本文利用SRAM作为外部缓存存储器。采用分场分区存储技术,使刷新频率大为提高,图像显示效果清晰稳定,实现了分辨率800×256,刷新频率90 Hz,红绿蓝三色256×256×256灰度级的视频显示系统。同时,采用该技术,亮度和灰度级方便可调,亮度损失小。

2 系统组成

LED视频显示系统总体框图如图1所示:该系统由发送和接收两部分组成,发送部分的功能主要是对DVI接口传输的视频信号进行编解码形成24 b真彩色视频数据和点时钟(CLK),行同步信号(HS),场同步信号(VS),数据有效信号(DE)等控制信号,通过LVDS(Low Voltage Differential Signaling)电平传输到接收卡上,经过接收卡的数据处理传送给具有特定驱动结构(1/8扫描方式,74HC595驱动芯片)韵LED大屏。本文的重点是介绍接收卡的数据处理模块。

数据处理流程如图2所示:接收卡接收发送卡传输过来的视频信号(控制信号和数据信号),将视频信号中的数据经过位面分离,分场存入外部缓存,然后分区读出,传送给显示驱动屏。其中位面分离模块将不同数据的同权位重新组合成新的数据存储在存储器中。外部缓存采用两个SRAM乒乓缓存的技术,实现数据的流水线处理。下面分别介绍位面分离模块和分场分区存储的原理和实现。

视频显示屏采用的灰度级控制方式为分场叠加与占空比相结合的方式,如表1所示:其中分场叠加是指用不同场次的恒频扫描来实现不同灰度级,如表1的D7~D4;占空比控制是指控制点亮时间与关断时间的占空比来实现灰度的调节,如表1的D3~D0。而这两种方式的前提都是要实现视频数据的位面分离。位面分离用FPGA来实现,一共包括两大模块,数据移位寄存器和数据选择器。用VHDL实现的原理框图如图3所示,其中r0-7,g0-7,b0-7分别是真彩色图像数据的红绿蓝三色,分别占用一个字节。把这24位数据线分别通过一个8位宽数据移位寄存器寄存,然后通过一个颜色位选择器输出到外部缓存器中。通过控制缓存器的地址实现位面分离,外部缓存的数据宽度为24位,使RGB三种颜色并行进行位面分离。其中移位寄存器使用了流水线的技术,在锁存输出前8个数据的同权位的同时,移进第9个数据的同权位,这样提高了数据处理的效率。

3.2 分场分区存储

数据经过位面分离以后,不同数据的同权位组成了新的数据,通过控制存储器的地址使一帧所有数据的同权位写在存储器的同一段中,因此对写地址发生器要求比较高。该系统要求256级灰度,那么将存储器分成8个段,每个段存储代表同一个权值的位(场)。其中,8个段用3(23)根地址线来代替,分辨率为800*256的大屏有256行,800列,那么行地址用8(28)根地址线表示,这8根地址线前5位为区地址(32区),后3位为一个区的行地址(1/8扫描)。列地址用7(27)根地址线来表示,因为存储器为24位宽,一个存储单元代表LED显示屏8个RGB点的同权位,其优先级从高到底的顺序为:场地址>列地址>行地址。分别用计数器来实现,这三个计数器级联就构成了存储器的写地址,其连接方式为:场地址(A17~A15),区地址(A14~A10),区内行地址(A9~A7),列地址(A6~A0)。由此可见,通过改变存储器地址线的优先级可实现分场(8场)存储。

数据分8场写入存储器,读出时要求分19场读出,并且要控制每一场的显示时间。所以在产生读地址的场地址计数器的时候,先设计一个19进制的计数器counter19(0~18)。表2为counter19和场地址计数器的关系:每一场的显示时间是用比较器来实现的,可以通过改变比较器中的值灵活地校正灰度和亮度。

- 高速DAC AD9712B/AD9713B的原理和应用(11-30)

- OLED技术会铺平通向微显示器之路吗?(05-18)

- 视频解码器SAA7111在图像采集中的应用(06-21)

- 锁相环同步检波技术及在视频检波中的应用(05-20)

- 基于CPLD的VGA视频显示系统的设计(05-16)

- 视频编码讲坛之H.264前世今生(05-18)