用CMOS技术实现高速模数转换器

时间:10-18

来源:EDN

点击:

通信用接收器的发展趋势是必需在信号刚一进入接收器信号通道时就进行取样,并配备有精确的测试仪,而要达到这个目标就要依赖超高速模拟数字转换器来实现。美国国家半导体|0">半导体首推的 ADC081000 芯片是一款模拟输入带宽高达 1.8 GHz 的 8 位 1GSPS 模拟数字转换器,它采用 0.18 微米 (mm) 的互补金属氧化半导体 (CMOS) 工艺技术制造。下文简述了结构及动作的原理,并较详细介绍了上文提到的在动作过程中起什么重要作用。

环顾目前的市场,大部分超高速模拟数字转换器都采用双极互补金属氧化半导体 (BiCMOS) 工艺技术制造,因此 ADC081000 芯片是市场上第一款完全采用 CMOS 技术制造的模拟数字转换器产品。由于双极晶体管的补偿电压比 CMOS 晶体管低,而增益则较高,因此工程师一向喜欢采用双极芯片设计模拟数字转换器前端,例如取样及保持放大器等信号调节电路。对于需要支持高频率操作的系统来说,双极芯片尤其受工程师欢迎。但双极芯片的缺点是需要较高的供电,其功耗远比采用 CMOS 技术的同类芯片大。ADC081000 芯片的实际功耗只有 1W 左右。相比之下,市场上功耗最低的 BiCMOS 模拟数字转换器则耗用超过 3W 的功率。要装设怎样的散热器才可将如此大量的热量全部散发?这却是一个令人极为头痛的问题。ADC081000 芯片不但性能卓越,而且符合通信系统及高性能测试仪表所需的动态规格,可提供 7 以上的有效位数 (ENOB),远超尼奎斯特(nyquist)的规定。

结构及运作原理

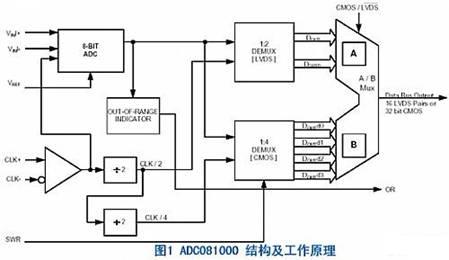

高速模拟数字转换器有多种结构可供选择,其中以快闪式、流水线式或折叠/内插式等三种最受欢迎。采用快闪式及折叠/内插式的结构可让数字 CMOS 工艺发挥更大的灵活性。折叠式模拟数字转换器的优点是速度快,而且所需的比较器比快闪式模拟数字转换器少。内插式模拟数字转换器则只需极少量输入放大器,而且所需的输入电容也较低。我们所知的折叠/内插式结构便是这两种技术的集成,其优点是管芯体积较小、功耗较低、而动态性能又很高,因此 ADC081000 芯片便采用这种结构,图 1 所示的就是这款芯片的结构框图。

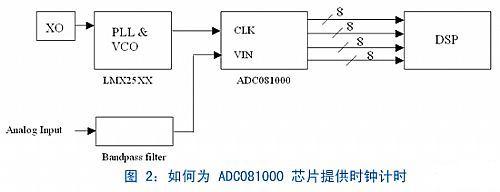

以 ADC081000 这类高速、高性能的集成电路来说,它们所需的时钟信号绝对不能附随任何噪音,以确保外部时钟不会将不受欢迎的噪音带进系统,影响系统的整体动态性能。ADC081000 芯片所需的时钟必须属于低相位噪音 (低抖动) 时钟,而且必须能以千兆赫 (GHz) 以上的频率操作。传统的石英振荡器虽然可以提供低抖动的时钟信号,但市场上只有极少石英振荡器能提供振荡频率超过几百兆赫 (MHz) 的时钟信号。为了确保振荡频率及低相位噪音符合要求,我们可以采用高频率压控振荡器 (VCO)、锁相环路 (PLL) 及石英振荡器,并按图 2 所示的设计将之集成一体,这是目前最佳的方法。

面对每秒 1Gbps 的数据传输速度,我们有什么对策?

为了方便捕捉输出数据,ADC081000 芯片设有低电压差分信号传输 (LVDS) 及 CMOS 两种操作模式。(下文将会简单介绍 LVDS 技术的运作原理)。我们只要将逻辑高电平或逻辑低电平连接管脚 1,便可选择要求的模式。采用 LVDS 模式操作时,内部的 1:2 多路分配器负责为两个输出总线馈电,以及将输出数据速度降低至只有取样率的一半。采用 CMOS 模式操作时,内部的 1:4 多路分配器负责为四个输出总线馈电,以及将输出数据速度降低至只有取样率的四分之一。各总线上的数据会同时交错处理,使每一总线能分别以 500MSPS 及 250MSPS的速度输出数据,令数据输出速度合计高达 1GSPS。无论采用 LVDS 还是 CMOS 的模式操作,系统必须提供一个或多个与输出数据传送过程同步的输出时钟,以便简化数据捕捉过程。

环顾目前的市场,大部分超高速模拟数字转换器都采用双极互补金属氧化半导体 (BiCMOS) 工艺技术制造,因此 ADC081000 芯片是市场上第一款完全采用 CMOS 技术制造的模拟数字转换器产品。由于双极晶体管的补偿电压比 CMOS 晶体管低,而增益则较高,因此工程师一向喜欢采用双极芯片设计模拟数字转换器前端,例如取样及保持放大器等信号调节电路。对于需要支持高频率操作的系统来说,双极芯片尤其受工程师欢迎。但双极芯片的缺点是需要较高的供电,其功耗远比采用 CMOS 技术的同类芯片大。ADC081000 芯片的实际功耗只有 1W 左右。相比之下,市场上功耗最低的 BiCMOS 模拟数字转换器则耗用超过 3W 的功率。要装设怎样的散热器才可将如此大量的热量全部散发?这却是一个令人极为头痛的问题。ADC081000 芯片不但性能卓越,而且符合通信系统及高性能测试仪表所需的动态规格,可提供 7 以上的有效位数 (ENOB),远超尼奎斯特(nyquist)的规定。

结构及运作原理

高速模拟数字转换器有多种结构可供选择,其中以快闪式、流水线式或折叠/内插式等三种最受欢迎。采用快闪式及折叠/内插式的结构可让数字 CMOS 工艺发挥更大的灵活性。折叠式模拟数字转换器的优点是速度快,而且所需的比较器比快闪式模拟数字转换器少。内插式模拟数字转换器则只需极少量输入放大器,而且所需的输入电容也较低。我们所知的折叠/内插式结构便是这两种技术的集成,其优点是管芯体积较小、功耗较低、而动态性能又很高,因此 ADC081000 芯片便采用这种结构,图 1 所示的就是这款芯片的结构框图。

以 ADC081000 这类高速、高性能的集成电路来说,它们所需的时钟信号绝对不能附随任何噪音,以确保外部时钟不会将不受欢迎的噪音带进系统,影响系统的整体动态性能。ADC081000 芯片所需的时钟必须属于低相位噪音 (低抖动) 时钟,而且必须能以千兆赫 (GHz) 以上的频率操作。传统的石英振荡器虽然可以提供低抖动的时钟信号,但市场上只有极少石英振荡器能提供振荡频率超过几百兆赫 (MHz) 的时钟信号。为了确保振荡频率及低相位噪音符合要求,我们可以采用高频率压控振荡器 (VCO)、锁相环路 (PLL) 及石英振荡器,并按图 2 所示的设计将之集成一体,这是目前最佳的方法。

面对每秒 1Gbps 的数据传输速度,我们有什么对策?

为了方便捕捉输出数据,ADC081000 芯片设有低电压差分信号传输 (LVDS) 及 CMOS 两种操作模式。(下文将会简单介绍 LVDS 技术的运作原理)。我们只要将逻辑高电平或逻辑低电平连接管脚 1,便可选择要求的模式。采用 LVDS 模式操作时,内部的 1:2 多路分配器负责为两个输出总线馈电,以及将输出数据速度降低至只有取样率的一半。采用 CMOS 模式操作时,内部的 1:4 多路分配器负责为四个输出总线馈电,以及将输出数据速度降低至只有取样率的四分之一。各总线上的数据会同时交错处理,使每一总线能分别以 500MSPS 及 250MSPS的速度输出数据,令数据输出速度合计高达 1GSPS。无论采用 LVDS 还是 CMOS 的模式操作,系统必须提供一个或多个与输出数据传送过程同步的输出时钟,以便简化数据捕捉过程。

- 用LatticeXP FPGA 桥接吉比特媒体独立接口(01-18)

- 让LM1875声音更靓(02-07)

- 适合LIN总线控制车门区域应用的高级电源管理器件(02-01)

- 现代通信系统电源设计(02-13)

- 便携式应用处理器设计中的电源管理(03-02)

- 利用智能交流电控制增加家电系统的安全性(04-23)