CMOS集成电路中ESD保护技术研究

时间:10-17

来源:中电网

点击:

针对ESD放电的瞬间电压快速变化,借助电容耦合(coupling)作用使ESD防护电路达到更有效率的保护能力。

在亚微米工艺下,输入/输出PAD处的ESD保护用的MOS一般W/L的值较大,在布局上经常画成叉指结构。但是,在ESD放电发生时,各个叉指不一定会同时导通,若只有2~3支叉指先导通,ESD电流便集中流向这2~3支叉指,该器件的ESD防护能力等效于只有2~3支叉指的防护能力。为克服大尺寸晶体管不均匀导通的情况,可以利用电容耦合作用来使大尺寸晶体管的每一叉指都能均匀地导通。

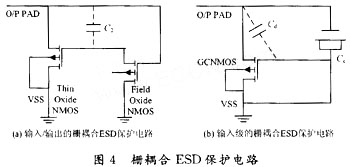

图4(a)利用电容耦合作用使大尺寸晶体管均匀导通,NMOS的杂散Cgd电容做耦合器件,通过场氧NMOS加强了耦合电容的效用,当正的ESD电压突然出现在PAD上时,由于电容耦合作用NMOS栅极电压跟着上升,故大尺寸NMOS均匀导通而进入骤回崩溃区(snapback region),ESD放电能量便可均匀分散到每一叉指来承受,真正发挥大尺寸晶体管器件应有的ESD防护水准。

图4(b)是电容耦合技术应用于输入级ESD防护电路上的一种安排,GCNMOS(Gate-Couple NMOS)是ESD电流旁通用的器件,尺寸较大。

因应用在输入端,故其栅极需经电阻Rg(~10 kΩ)接地,以使该GCNMOS在CMOSIC工作时是关闭的。另有-NMOS连接成电容状Cc加强电容耦合作用。当有正的ESD电压在输入PAD上发生时,一部分的正电压会经由Cd与Cc耦合到GCNMOs的栅极,栅极电压会经由Rg放电到地去,Rg的大小会影响栅极电压的维持(Holding)时间。GCNMOS因而可以达到均匀导通的目的,以提升其ESD防护能力。

3 结 语

MOS集成电路ESD保护电路基于工艺级别、器件级别和电流级别的改进,已有大量优秀的ESD保护电路出现,ESD保护电路强度已超过2 000 V(采用HBM模型试验)。几种方法结合制造的ESD保护电路,如采用栅耦合PTLSCR/NTLSCR ESD保护电路,可有效的对深亚微米CMOS IC薄栅氧化层保护,而且占用的版图面积只占传统ESD保护电路的1/2左右。

- 德州仪器高性能模拟运放产品系列介绍集锦(11-13)

- CMOS求和比较器在PWM开关电源控制中的应用(11-27)

- 如何将CMOS LDO应用于便携式产品中(01-15)

- 2.5 Gb/s 0.35μmCMOS光接收机前置放大器设计(01-22)

- 用于下一代移动电话的电源管理划分(08-28)

- 不同电源供电的器件间的桥接(04-27)