LCoS显示芯片的研制

时间:08-17

来源:电子技术应用

点击:

LCoS(硅基液晶)作为新型显示器件,具有大屏幕、高亮度、高分辨率、省电等诸多优势,用LCoS技术制作高分辨率光阀的方法逐渐在平板显示界占有一席之地[1]。本文设计的用于三片式彩色投影机的高集成化LCoS显示芯片,采用标准0.6μm-四层金属-双电源CMOS工艺设计和制作,其空间分辨率为800×600像素,目前已在国内半导体生产线上小批量成功流片。

1 LCoS显示器件的物理结构与性能

LCoS显示器是一种反射式光调制器,不影响入射光到每个像素的截面积,从而大大提高了开口率[2]。笔者设计的三片式投影显示系统采用空间混色法实现彩色化,即分别用三片LCoS芯片控制红绿蓝三基色图形,然后通过光学系统实现空间混色。

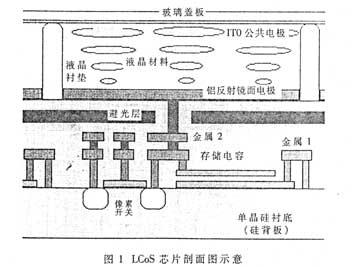

笔者采用标准0.6μm-n阱-四层金属CMOS工艺设计的单色LCoS器件物理结构剖面图如图1所示。图中,把金属3设计成避光层,金属4设计成反射镜面电极,其目的是使金属3和4交叠遮盖显示矩阵的有源部分,从而完全挡住了入射光线,降低了NM0S晶体管源极PN结上产生的光生漏电流。这种设计可防止因此而引起的图像对比度退化。

为了提高本次设计的成功率,采用投影显示系统中主流产品的显示性能指标(见表1)。这样,一方面不会因为芯片电路结构的复杂性,使得设计难度大幅度地增加,而转移本科研的注视点;另一方面,若这种模拟式单色显示方式能成功实现,可直接与主流产品接轨。

图2给出了LCoS芯片的电路结构框图。总体上芯片电路可划分为行扫描驱动器、列数据驱动器和显示像素矩阵。为了降低芯片工作频率,同时利于周边驱动电路布局布线,把列数据驱动器分成电学结构完全一致的上下两组,分别驱动奇偶数据线。

单色LCoS芯片采用视频信号电极逐场反转模式,即作用在像素电极上的信号电平相对于上盖玻璃基片上公共电极的电压,每一帧都改变一次极性,于是视频信号成为周期性改变的交流电压,从而可以防止液晶材料的电化学退化。

3 采用EDA技术设计LCoS芯片

从前面的分析可以发现,LCoS芯片不可能直接采用标准单元、门阵列等半定制方法来实现。实际上,LCoS芯片的物理版图实属LSI级,其设计过程十分复杂,较好的设计策略是采用层次设计与EDA设计相结合的方法,基本的设计过程是采用自顶向下的设计。具体地说,使用具备全定制设计功能的Cadence EDA设计工具,按照"自顶向下"的规则来设计LCoS芯片的版图。首先确定微显芯片的功能、性能、允许的芯片面积和成本等;接着进行结构设计,分化出尽可能简单的子系统;然后把各子系统间的逻辑关系转换成电路图,进行电路逻辑设计和电路仿真;最后采用全定制方法综合出整个LCoS芯片版图。设计好的版图还要通过提取版图的结构信息和寄生参数信息与原来的结构描述相比较,验证它们之间的一致性。

3.1 数据准备

笔者采用具有4层金属布线的CMOS工艺路线来实现LCoS芯片。为此首先在Cadence环境下编写与Diva验证工具相匹配的工艺文件(LCoS.tf)[4]。其中包括:①LCoS芯片光刻版图层及其属性的定义;②符号元件;③DRC、ERC、LVS检查规则;④寄生电阻、电容提取规则;⑤抽象单元规则。

3.2 建立LCoS显示芯片的单元库

笔者为LCoS显示芯片建立的基本单元包括:反相器、门电路、准静态D触发器、模拟电子开关、基本运算放大器、电平变换器以及各种应用的I/O单元[5]。考虑到各基本单元的逻辑功能不同,其版图面积的大小也不可能一样,因此规定列方向上的基本单元,其宽度一致;而在行方向上的基本单元,其高度一致;并且与显示矩阵的规则排列相一致。这为整个版图的快速组合铺平了道路。

3.3 版图布局策略

布局是指将模块安置在芯片上的适当位置,并能满足一定的目标函数。由于LCoS显示芯片在整体物理结构方面具有严格的横向或纵向对称性,可以免去那些在常规半导体版图设计中采用的顶层规划与底层规划。当运用LCoS显示芯片的单元物理视图完成单行或单列的版图优化时,可在Cadence平台上设置LCoS显示矩阵截距,然后反复复制单行或单列的物理视图来实现LCoS显示芯片的主要版图布局规划。图3是笔者在Cadence平台上规划出的LCoS(SVGA分辨率)显示芯片版图,图中像素截距设计为16μm,其芯片对角线保持在21mm(约0.83英寸)左右。

1 LCoS显示器件的物理结构与性能

LCoS显示器是一种反射式光调制器,不影响入射光到每个像素的截面积,从而大大提高了开口率[2]。笔者设计的三片式投影显示系统采用空间混色法实现彩色化,即分别用三片LCoS芯片控制红绿蓝三基色图形,然后通过光学系统实现空间混色。

笔者采用标准0.6μm-n阱-四层金属CMOS工艺设计的单色LCoS器件物理结构剖面图如图1所示。图中,把金属3设计成避光层,金属4设计成反射镜面电极,其目的是使金属3和4交叠遮盖显示矩阵的有源部分,从而完全挡住了入射光线,降低了NM0S晶体管源极PN结上产生的光生漏电流。这种设计可防止因此而引起的图像对比度退化。

为了提高本次设计的成功率,采用投影显示系统中主流产品的显示性能指标(见表1)。这样,一方面不会因为芯片电路结构的复杂性,使得设计难度大幅度地增加,而转移本科研的注视点;另一方面,若这种模拟式单色显示方式能成功实现,可直接与主流产品接轨。

图2给出了LCoS芯片的电路结构框图。总体上芯片电路可划分为行扫描驱动器、列数据驱动器和显示像素矩阵。为了降低芯片工作频率,同时利于周边驱动电路布局布线,把列数据驱动器分成电学结构完全一致的上下两组,分别驱动奇偶数据线。

单色LCoS芯片采用视频信号电极逐场反转模式,即作用在像素电极上的信号电平相对于上盖玻璃基片上公共电极的电压,每一帧都改变一次极性,于是视频信号成为周期性改变的交流电压,从而可以防止液晶材料的电化学退化。

3 采用EDA技术设计LCoS芯片

从前面的分析可以发现,LCoS芯片不可能直接采用标准单元、门阵列等半定制方法来实现。实际上,LCoS芯片的物理版图实属LSI级,其设计过程十分复杂,较好的设计策略是采用层次设计与EDA设计相结合的方法,基本的设计过程是采用自顶向下的设计。具体地说,使用具备全定制设计功能的Cadence EDA设计工具,按照"自顶向下"的规则来设计LCoS芯片的版图。首先确定微显芯片的功能、性能、允许的芯片面积和成本等;接着进行结构设计,分化出尽可能简单的子系统;然后把各子系统间的逻辑关系转换成电路图,进行电路逻辑设计和电路仿真;最后采用全定制方法综合出整个LCoS芯片版图。设计好的版图还要通过提取版图的结构信息和寄生参数信息与原来的结构描述相比较,验证它们之间的一致性。

3.1 数据准备

笔者采用具有4层金属布线的CMOS工艺路线来实现LCoS芯片。为此首先在Cadence环境下编写与Diva验证工具相匹配的工艺文件(LCoS.tf)[4]。其中包括:①LCoS芯片光刻版图层及其属性的定义;②符号元件;③DRC、ERC、LVS检查规则;④寄生电阻、电容提取规则;⑤抽象单元规则。

3.2 建立LCoS显示芯片的单元库

笔者为LCoS显示芯片建立的基本单元包括:反相器、门电路、准静态D触发器、模拟电子开关、基本运算放大器、电平变换器以及各种应用的I/O单元[5]。考虑到各基本单元的逻辑功能不同,其版图面积的大小也不可能一样,因此规定列方向上的基本单元,其宽度一致;而在行方向上的基本单元,其高度一致;并且与显示矩阵的规则排列相一致。这为整个版图的快速组合铺平了道路。

3.3 版图布局策略

布局是指将模块安置在芯片上的适当位置,并能满足一定的目标函数。由于LCoS显示芯片在整体物理结构方面具有严格的横向或纵向对称性,可以免去那些在常规半导体版图设计中采用的顶层规划与底层规划。当运用LCoS显示芯片的单元物理视图完成单行或单列的版图优化时,可在Cadence平台上设置LCoS显示矩阵截距,然后反复复制单行或单列的物理视图来实现LCoS显示芯片的主要版图布局规划。图3是笔者在Cadence平台上规划出的LCoS(SVGA分辨率)显示芯片版图,图中像素截距设计为16μm,其芯片对角线保持在21mm(约0.83英寸)左右。

- 基于DSP的液晶显示若干问题的探讨(06-02)

- 便携式单片机控制液晶显示型心率计(03-12)

- 基于DSP的彩色TFT-LCD数字图像显示技术研究(05-05)

- MAX7219驱动LED显示器显示连续数的方法(05-06)

- OLED技术会铺平通向微显示器之路吗?(05-18)

- 大屏幕LED 点阵显示系统(05-24)