电源完整性与地弹噪声的高速PCB仿真

图4,其变化幅度取决于电路板的阻抗和芯片偏置管脚处的用于提供电流的退耦电容;为了避免电压的尖峰波动,在从直流到信号带宽的频率范围内,Z值必须低于某一门限值。图中虚线部分即为PDS阻抗应该满足的目标区域。

在该设计中,为了保持电源完整性,电源-地的电压波动必须保持在标准值3.3V的5%以内。因此噪声不能大于0.05×3.3V=165 mV。可以据此按照欧姆定律计算出PDS的最大阻抗165mV/2A=82.5mΩ,图4中虚线部分即为PDS阻抗应该满足的目标区域。

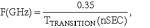

对于最低频率,通常是1kHz或者更低的频率--电源满足阻抗特性的要求,电源和地层的结构通常不会破坏阻抗特性,因为它们呈现低电阻与电感特性。而当频率高于1kHz时,电流通路的互感大到足以使电压超过限定值,根据:

对于更高的频率,退耦电容作为电源层与地层之间的低阻抗连接是必要的。需要满足PDS阻抗要求的信号带宽可由下式估计:

在该设计中,其带宽为1.75GHz。

为了达到这么宽的带宽,通常需要在MHz信号区域放置很多高频瓷片电容,在kHz信号区域放置体积较大的电解电容。这些电容矩阵与其它器件共同占用宝贵的电路板空间。在反复试验的设计方法中,物理原型是不可缺少的,而虚拟原型技术使设计者可以在不需要物理原型的基础上解决这个问题。

为PCB板设计PDS,例如此例中的xDSM板,使用SIwave可以在IC芯片处放置一个端口,计算电路板在适当带宽内的输入阻抗。图5中红色曲线显示的是电路板上无电容时的阻抗。阻抗轴与频率轴都取对数坐标。仿真显示了电路板本身电容的影响而忽略了经过电源的低感应电流回路。从图中可以看出,阻抗随着频率的减少而增加,但由于经过电源的回路也有低阻抗,因此这种关系并不是严格的。

图5,红色曲线显示的是电路板上无电容时的阻抗;深蓝色曲线是经过重新设计后的阻抗特性;浅蓝色曲线是又增加10nF电容矩阵后的阻抗曲线;绿色曲线表示再次增加1nF电容矩阵后的结果。

根据Z=1/(j•C),红色曲线中的直线部分表明电路板本身的电容为74nF。为了使阻抗在1MHz处低于目标阻抗82.5mΩ,电容值至少应为 2μF--几乎是电路板本身电容的30倍。为此首先需要增加22个0.1μF的电容矩阵。图中深蓝色曲线是经过重新设计后的阻抗特性。在大多数的频率范围内,设计满足了阻抗特性的要求。但在带宽的高端,电容的ESL(等效串联电感)、ESR(等效串联电阻)以及由电容间距带来的附加电感使阻抗曲线没有达到阻抗特性要求。

由于更小的电容具有更小的ESL和ESR值,因此增加旁路有助于提高其高频特性。图5中的浅蓝色曲线是又增加10nF电容矩阵后的阻抗曲线。绿色曲线表示再次增加1nF电容矩阵后的结果。每一级别电容矩阵的增加都提高了阻抗特性,但结果仍然刚刚满足阻抗特性的要求。

在设计的这个阶段,设计者可以增加电磁仿真与电路仿真一起来完成设计。这种方法使设计者可以精确地为低端的阻抗建模,包括电源的负载效应。它也可以直接仿真电源管脚上的噪声从而直接验证电源层噪声,避免对电源层阻抗的过多分析导致的不必要的设计开销。

首先应在选定的位置添加输入和输出端口。上文已经在一个IC芯片处添加了端口,接着应该在电源输入端添加一个端口,同时在其它两块芯片的安装位置添加两个端口。然后在SIwave中你可以进行宽频扫描,在整个带宽内获得4×4的S参数散射矩阵。接下来可以使用Full-Wave Spice产生与Spice兼容的电路文件以便在电路仿真环境中进一步分析。

在产生的电路文件中,PCB板在电路的中心位置。电路文件还包括 FPGA的模型--伴有一个电流探针和一个差分电压探针的电流源。Full-wave Spice创建的Spice电路还包括上文提到的三个电容矩阵。如果在IC处再增加第四个电容矩阵将进一步减小高端阻抗。电路还包括一个直流电源,电源伴有少量容值从1nF到100μF的退耦电容。另外还包括其它两个IC芯片的模型,周围伴有少量100nF的电容矩阵。

图6,蓝色和绿色曲线分别表示在没有添加和添加最后一组电容矩阵后IC芯片的电源完整性曲线;红色曲线代表芯片输入电流的突变。

图6显示了FPGA的电源电压的噪声仿真结果。红色曲线代表芯片输入电流的突变--在0.2纳秒内电流由0A变化到2A。蓝色曲线表示没有添加最后一组电容矩阵时IC芯片的电压曲线。与3.3V相比,电压的波动已经很小了,但还是超过了5%的规范要求。绿色曲线表示添加了第四组电容矩阵后电压的波动曲线,最终的设计满足了电源噪声小于165mV的规范要求。

可以用同样的方法分析电路板上其它的芯片,保证他们不受电源压降和地弹的影响。在本例中另外两芯片分别吸收100mA和50mA电流,相对来说,它们对噪声的贡献是很小的。

高速电路的PCB板级设计是十分具有挑战性的。为了保证电路的正确工作,需要精心设计电路的PDS,包括在电路板上添加数以百计的退耦电容,并且根据需要选择合适的电容值及其位置。采用对虚拟原型进行仿真的方法替代反复试验的设计方法来优化电路板的电源完整性设计,可以有效缩短设计周期并且节约设计成本。

- 高速PCB中电源完整性的设计(09-27)

- 电源系统的电磁兼容性设计(01-20)

- 电源完整性仿真让电路板更完美(02-23)

- 电源完整性设计之ESR对反谐振的影响(12-14)

- 电源管理总线的结构与优势(11-19)

- 如何设计一个合适的系统电源(上)(11-20)