不同电源供电的器件间的桥接

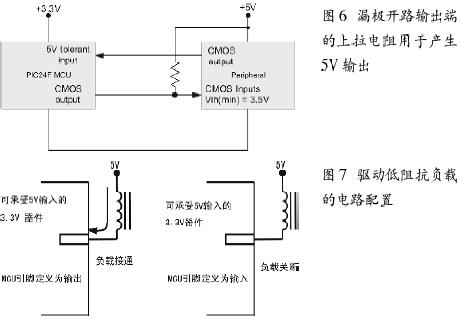

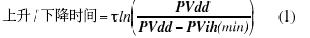

当采用上拉电阻配置(见图6)时,需要考虑两个器件间的连接电容,从而确定端口引脚处信号的上升/下降速率(和最大开关频率),以及适用的电阻值。考虑下面的公式:

其中 τ = RC 时间常数,R×C

PVdd = 外设电压Vdd

PVih(min) = 外设的 Vih(min) 值

如果使用下述典型值:

上拉电阻 R = 1K

电容 C(由于引脚和PCB电容) = 10pF

PVdd = 5V

PVih(min) = 0.7×Vdd = 3.5V

则上升/下降时间≈12nS

如果可接受的最小上升/下降脉冲的时间宽度50nS,那么最大的输出频率为20MHz。对于大多数外设互连来说,这已经足够了。

这种方法有一个缺点就是当MCU驱动逻辑低电平时,会通过上拉电阻消耗额外的电流。因此设计时需要考虑速度和电流大小两个因素折衷选择上拉电阻。需要为您的应用选择一个折衷的电阻值来提供所需的速度并且确保消耗的电流不超出规范。

有些人可能认为不能采用这类配置来驱动低阻抗负载。如果希望驱动一个5V的继电器,那么应当怎么做?幸运的是,对于驱动继电器这样的低阻抗负载,上述特性也有帮助。从图7了解电路配置信息。要驱动此类负载,需要将引脚定义为输出并驱动为低电平。这里,唯一的限制因素是器件的灌电流能力。要关断负载,将引脚定义为输入就可以了。关断负载会将5V电压直接馈入输入引脚。由于引脚可以承受5V电压,因此这一操作是正确的。换句话说,需要保持输出锁存器为逻辑低,并通过切换TRIS(输入/输出控制寄存器)来使负载接通/关断。

本文介绍了桥接由5V和3.3V供电的电路的有效方法。这些方法完全可以和转换阶段桥接由不同电压供电的电路的低成本智能解决方案媲美。同时,大多数器件很可能会很快转向使用更低的电源,从而不再需要进行电路桥接。本文给出的方法对于充分利用半导体行业的最新发展趋势以及降低系统成本肯定会有所帮助。

- 德州仪器高性能模拟运放产品系列介绍集锦(11-13)

- CMOS求和比较器在PWM开关电源控制中的应用(11-27)

- 如何将CMOS LDO应用于便携式产品中(01-15)

- 2.5 Gb/s 0.35μmCMOS光接收机前置放大器设计(01-22)

- 用于下一代移动电话的电源管理划分(08-28)

- CMOS功率放大器厂商加紧挑战GaAs(07-14)