基于USB2.0接口的语音采集系统设计

引言

语音信号的采集和处理在网络、通信、智能仪表、工业控制、医疗卫生、公共安全等领域得到了越来越广泛的应用,而这些工作都需要一套高速的语音信号采集系统来完成,要对语音进行采集就需要一种高速的,能进行长时间、大吞吐量数据传送的计算机接口。USB2.0接口就是一种符合语音采集要求的计算机接口,同时,它还具有支持热插拔、占用系统资源少、易于扩展、使用方便等优点。DSP是利用专门或通用的数字信号处理芯片,以数字计算的方法对信号进行处理,具有处理速度快、灵活、精确、抗干扰能力强、体积小及可靠性高等优点,可满足对信号快速、精确、实时处理及控制的要求,本采集卡采用TI公司高精度浮点DSP芯片TMS320C6713作为主控制器,采用高精度数字编解码芯片TLV320AIC23B实现ADC功能,使用Cypress公司EZ-USB SX系列中CY7C68001作为USB接口芯片,与传统语音采集卡相比,在实现相同的性能条件下该采集卡成本进一步降低,使用更方便,具有很高的性价比。

1 系统硬件设计

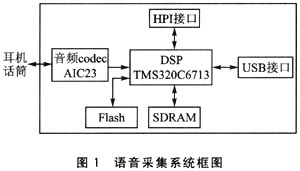

语音采集系统是在TMS320C6713(简称"C6713")平台上设计开发的,该平台的系统框图如图1所示。

该系统的总体设计任务:由主机的应用程序通过USB总线传输发出命令,控制采集卡对语音信号的采集、播放、数据传输和语音回放;同时根据采集卡返回的状态字显示语音采集卡的工作情况,语音采集过程:DSP控制TLV320AIC23B(简称"AIC23")对语音信号进行采样,采样得到的数据,再经过DSP与USB之间的数据传输通道传送至USB接口芯片,再传送到主机上存储,语音回放过程:主机把处理后的数据传给USB接口芯片,DSP通过与USB之间传输通道取数据,然后将数据传给D/A转换器,经D/A转换后输出。

USB芯片CY7C68001实现主机和DSP外设的高速数据通信,DSP作为控制器和系统的快速处理得执行者,主要任务是根据主机传来的命令或参数,以尽快的速度完成数据传送。本卡将CY7C68001配置在C6713的EMIF的CE3空间,采用CY7C68001的异步读/写方式完成二者之间数据和命令的交换,CY7C68001除了存储器接口外,还有1个中断信号(USBINT)和4个状态信号(READY、FLAGA、FLAGB和FLAGC)及中断信号USBINT使用C6713的外部中断EXT_INT5;同时USBINT中断还被映射到板卡的控制状态寄存器(UN_REG)中,供C6713查询,以确定真正的中断源,C6713是通过EMIF来完成CY7C68001的数据与命令的交换,在XC9572XL内部构造时序逻辑来完成DSP与USB芯片的通信。其连接如图2所示。

AIC23有2个接口,一个是控制口,用于设置AIC23的工作参数,另一个是数据口,用于传输AIC23的A/D、D/A数据,这部分与C6713的MCASP无缝连接。连接电路如图3所示,在本卡中AIC23配置成主模式,AIC23的控制口使用2线制的I2C方式,其中CS的反是片选信号,低电平有效;SDIN是AIC23控制口串行数据输入,SCLK是AIC23控制口的位-时钟。数据口使用I2S方式,与DSP的MCASP0连接,其中,BCLK表示数据口位-时钟信号,LRCIN表示数据口DAC输出的帧同步信号,LRCOUT表示数据口ADC输入的帧同步信号,DIN表示数据口DAC输出的串行数据输入,DOUT表示数据口ADC输入的串行数据输出。BCLK由AIC23产生,MCASP0的发送与接收时钟均由AIC23来提供。

DSP外部扩展了2片现代半导体公司的(4 Bank×1M×16位)HY57V641620HGT-P SDRAM,提供DSP程序运行器件所需的动态存储空间。SDRAM的片选信号直接与DSP的EMIFA外设的信号相连,从而使SDRAM被映射到DSP的0x80000000-0x80FFFFFF地址范围内。在对SDRAM进行读/写访问前,需通过EMIF的控制寄存器CE0CTL将空间配置为32位SDRAM存储器接口,通过SDCTL、SDTIM、SDEXT等寄存器设置SDRAM的读/写时序和参数,DSP与SDRAM的连接如图4所示。

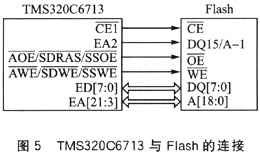

另外,扩展了AMD公司的一片Am29LV320D(4M×8位/2M×16位)Flash存储器,用于保存上电引导的用户程序。如果DSP采用ROM引导模式,则在DSP复位之后,DSP会把EMIF的CE1空间的1KB的ROM代码搬移到片内RAM空间,从而实现自举引导,所以本设计中把Flash的片选信号连接到了DSP的EMIF的引脚,从而使Flash映射到DSP的0x90000000-0x900FFFFF地址范围内。由于Flash是以8位进行访问的,所以其物理地质以8位为单位进行编址。DQ15/A-1引脚的"A-1"表示字节模式,故将EA2与DQ15/A-1引脚连接。Flash的接口示意图如图5所示。

2 软件设计

在USB固件的开发过程中,使用了固件架构来进行固件的开发,将整个程序按功能划分成了6个功能模块:主循环模块、厂商定义请求处理模块、标准设备请求处理模块、中断服务程序模块、命令接口模块和数据接口模块,DSP一旦上电就需要初始化PLL寄存器、EMIF寄存器、CSL库初始化和中断配置。设备上电后,主机通过设备的上拉电阻产生的信号变化来检测新的设备连接,然后判断CY7C68001是否准备好,如果准备好就打开中断,加载描述符,等待自举成功;一旦自举成功就初始化CY7C68001,检查事件标志并进入对应的模块程序做进一步的处理。主循环模块的流程如图6所示。