面向数字电视应用的负载点电源设计与分析

当前的数字电视为电源设计人员提出了若干挑战,这些电视机都是由位于机箱内部不同位置的独立模块组成的平板设计。这些模块包括调谐器单元、主系统板、显示驱动器、音频子系统、LCD 背光驱动器以及其它组件。每个子系统均包含敏感的模拟电路、处理器、CPU、ASIC 以及其它各种电路,而每个器件都具有自身独特的电源要求。交流电压先转换成中间总线电压,然后提供给电视机内部的各个模块。该电压的典型范围为12~15V。每个模块中的负载点稳压器均可将中间总线电压转换成每个组件所需要的电压。

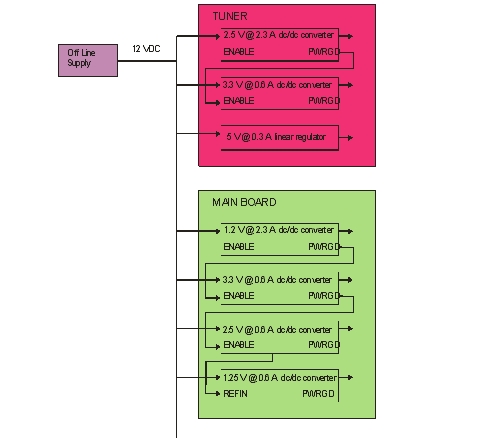

如图1所示的LCD TV结构图,机箱中的每个主要子系统都与关键组件模块一道在图中给出,本例中包括前端调谐器、主板、显示驱动器以及音频板。这些组件均由12V离线电源供电。为了提供所需的工作电压,必须在每个模块中提供某种形式的负载点稳压。表 1 中列出了每个子系统与模块对电压及电流的要求,以及所有附加要求,如排序或跟踪。

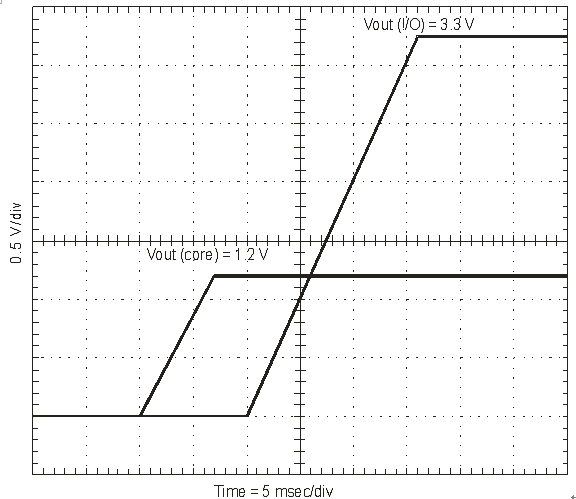

主板与显示驱动器单元中采用的高性能信号处理器件(如FPGA与DSP)需要能够产生不同内核电压与 I/O 电压的多个电源。电源的上电和关断顺序对器件的运行与长期可靠性都至关重要。电源排序可以采用三种方法:顺序排序、比例(ratio-metric)排序与同时排序。正确的排序方法取决于处理器的要求。本例采用顺序排序方法,在该方法中一个电源的输出开始升压并且稳定到最终的电压上,然后第二个电源的输出在一定时间延迟之后开始升压。

图2是一个说明顺序排序方法的例子。实现这种排序方案的一个好的方法是采用具备电源良好指示与使能功能引脚的器件,把第一个电源的电源良好输出连接至需要排序的第二个电源的使能引脚,确保信号具有正确极性。包含上述特性的大部分DC/DC转换器均需如此使用,它们具有一致的极性,而且信号可以直接配合。另外,还可以通过这种方式控制附加电源。

图 1:LCD电视内部电路组成结构图。

图 2:排序电源波形。

以双倍数据速率(DDR)存储器为例,DDR系统同时需要Vddq与Vtt电压轨。Vddq输出可以采用标准电源类型,但总线终结电压Vtt需要不同的电源类型。对于这些DDR总线终结电源,Vtt电压生成电路必须能够精确跟踪参考电压Vref,它是输出电源电压Vddq的50%。虽然Vddq 可以在2.50V额定值?200mV范围内变化,但是Vtt在任何负载与瞬态条件下都必须保持在 Vref?40mV 的范围内。生成Vtt的电路还必须能够在输出缓冲器(线路驱动器)处于逻辑高电平状态时吸入电流,在输出缓冲器处于低电平时输出电流。在电流吸入(current-sinking)模式下,流经输出电感器的电流在降压配置中颠倒正常方向。

表1:每个子系统与模块对电压及电流的要求。

吸入模式的切换过程与升压转换器类似,除了电流流入电源的输出端,在升压后流出至输入电源轨。控制电路在输出与吸入电流时都必须正常工作。专用转换器在这些应用中表现良好,因为它的设计目的就是用于需要电压跟踪的总线终结电路。

图3显示了一种可行的电源解决方案。对于各种子系统而言,它都融合了相关电源的要求,因此在每个负载点都可以采用单个稳压器,而且只需要通过机箱分配 12V 中间总线电压。

图3:电源系统架构。

本文小结

对于模拟调谐器而言,理想情况是电源采用线性稳压器。虽然效率会有所降低,但敏感的模拟级可能需要线性稳压器的噪声抑制功能。如果功耗比较重要,则可以把中间总线预先调节到较低的电压,同时可以采用低压降线性稳压器。DC/DC转换器是为处理器、ASIC与FPGA数字电路供电的最佳选择,这与线性稳压器相比DC/DC转换器能够提供更高效率与更低功耗,而且能够提供更大电流。使用具有使能与集成电源良好信号等附加功能的转换器可以大大简化内核与I/O电压的排序。工程师在设计时需要特别留意总线终结电压的特殊要求。

作者:

John Tucker

j-tucker@ti.com

应用工程师

德州仪器公司

德州仪器 相关文章:

- 8位高速A/D转换器TLC5510的应用(02-16)

- 改善平板显示器的音频性能(02-13)

- 运算放大器的选择(03-18)

- 单端数字音频放大器设计和应用考虑的要素(05-19)

- 为网络监控摄像机设计合适的电源(05-20)

- 改善可编程增益放大器性能的一个技巧(05-21)