AD/DA转换技术的发展历程及其趋势

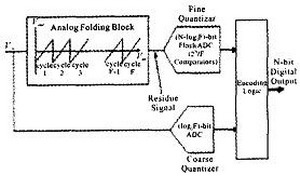

结构如图3所示,其基本原理就是通过一个特殊的模拟预处理(图3中的阴影部分)产生余差电压,并随后进行数字化,获得最低有效位(LSB),最高有效位(MSB)则通过与折叠电路并行工作的粗分全并行A/D转换器得到,几乎在对信号采样的同时,对余差进行采样。

图3 折叠结构框图

图3中,折叠电路的传输函数是理想情况,实际电路很难实现。所以,一般的折叠结构都具有非线性,但其过零点处的非线性为0。若只考虑这些过零点,则Vin与Vrj之差的极性可以被正确确定,再采用插值的办法产生额外的过零点来解决低位。这就是插值折叠的基本思想,它既利用了折叠特性,又不带来额外的非线性。

各种新技术的运用,使插值折叠型A/D转换器的性能不断提高。这里介绍两种新技术:电流式插值系统和级联结构。用电阻实现的电压式插值器,其精度受到电阻匹配度的限制,而在电流式插值器中,信号是由电流幅度表示的,其精度更高,而且更适合在低电源电压下工作。Li,Y-C等人通过在细量化通路上采用电流模式信号处理技术来降低电压摆幅,获得了具有300MSPS转换速度、60MHz输入信号带宽、7位分辨率的A/D转换器。另一种改进方法就是采用级联结构。在无需增加并行输入级和细分A/D转换器中比较器数目的条件下,级联结构可将转换精度提高到8位以上。

Vorenkamp,P.等人设计的12位插值折叠型A/D转换器采用三步式级联结构,其中,3位粗分量化,3位中分量化,6位细分量化。该A/D转换器只需50个比较器,转换速度为60MSPS。

流水线型模拟/数字转换

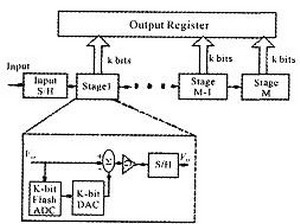

流水线型A/D转换器是对两步型A/D转换器的进一步扩展,其结构如图4所示。它将一个高分辨率的n位模拟/数字转换分成多级的低分辨率的转换,然后将各级的转换结果组合起来,构成总的输出。每一级电路由采样/保持电路(S/H)、低分辨率A/D转换器、D/A转换器、减法器和可提供增益的级间放大器组成。

图4 流水线型A/D转换器结构框图

这种类型的A/D转换器具有以下优点:每一级的冗余位优化了重叠误差的纠正,具有良好的线性和低失调;每一级都具有各自独立的采样保持放大器,因此允许流水线各级同时对多个采样进行处理,从而提高了转换速度;分辨率相同的情况下,电路规模及功耗大大降低。但它也存在一些缺点:复杂的基准电路和偏置结构;输入信号必须穿过数级电路,造成流水延迟;同步所有输出需要严格的锁存定时;对工艺缺陷和印刷线路板较敏感,这会影响增益非线性、失调及其它参数。

目前,普遍采用两种新技术来提高流水线A/D转换器的性能。一种是时间交织技术,使多条流水线并行工作。通过采用这种技术,可大大提高转换速率,但并行的通道数不能太多,否则,会大大增加芯片面积和功耗,而且各个通路之间需要高度匹配,在工艺上很难实现。Sumanen,L.等人设计了一个具有4个并行通道的流水线A/D转换器,采用0.5μmCMOS工艺实现。该A/D转换器的采样率高达200MSPS,分辨率为10位。另一种新技术就是数字校准技术,其主要思想是将校准周期内测量到的误差存放在存储器中,然后在正常运算周期内,通过原始码寻址,得到校对码,再通过原始码和校对码的运算,得到最终的数字输出。这种技术可对模拟电路的失调不匹配以及非线性引入的误差等进行有效的校正,从而使流水线A/D转换器的精度超过10位。Hakarainen,V.等人研制的交织型流水线A/D转换器,运用这种校正技术来校正子D/A转换器的误差,并对各并行通道之间增益和失调电压的失配进行补偿,从而在10位的器件匹配精度下获得了14位的转换精度。

逐次逼近型模拟/数字转换

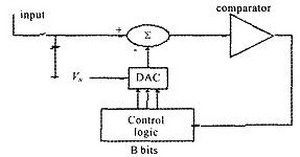

逐次逼近型A/D转换器的结构如图5所示,其工作原理如下:输入信号的抽样值与D/A转换器的初始输出值相减,余差被比较器量化,量化值再来指导控制逻辑是增加还是减少D/A转换器的输出;然后,这个新的D/A转换器输出值再次从输入抽样值中被减去,不断重复这个过程,直至其精度达到要求为止。由此可见,这种A/D转换器在一个时钟周期里只完成1位转换,N位转换就需要N个时钟周期,故它的采样率不高,输入带宽也较低;但电路结构简单,面积和功耗小,而且不存在延迟问题。

逐次逼近型A/D转换器的一个关键部分就是D/A转换器,它制约着整个A/D转换器的精度和速度。D/A转换器传统的制作方法是用精密电阻网络实现,但是它的精度不高。以电容阵列为基础,采用电荷重分布技术的D/A转换器可以获得更高的精度,这主要是由于在MOS电路中比较容易制造出小容量的精密电容,而且电容损耗极小。Gan,J-H等人采用非二进制的电容阵列结构实现D/A转换器,并采用自校准技术提高电容的匹配度,使D/A转换器的精度高达22位,制作出功耗为50mW的16位1.5MSPS高性能逐次逼近型A/D转换器。

图5 逐次逼近型A/D转换器结构框图

- 12位串行A/D转换器MAX187的应用(10-06)

- 低功耗、3V工作电压、精度0.05% 的A/D变换器(10-09)

- 12位串行A/D转换器的原理及应用开发(10-09)

- 在射击探测器中增加口径确定功能的简单电路(11-13)

- 一种折叠共源共栅运算放大器的设计(11-20)

- 深入解析:模拟前端模/数转换器的三种类型 (11-26)