Stratix II FPGA系统电源设计

转换效率较高的MAX1951作为电源转换。系统中的Stratix II FPGA所需电源有3.3 V和1.2 V两种,其中3.3 V用于I/O和PD,1.2 V用于内核与锁相环。

估算Stratix II的功耗时,首先应下载ALTERA网站提供的powerplay power estimator V5.1版(可支持Stratix II,Stratix II GX及HardCopy II的早期功耗估计);然后根据所选用的Stratix II FPGA种类、封装形式及用途来计算FPGA最大功率。本设计采用F484封装的EP2S30,经估算,其内核最大电流为0.467A,I/O最大工作电流为0.07A。这样就可以根据FPGA内核的工作频率、I/O资源的利用数量、PLL资源的利用数量、内部逻辑资源的利用情况、DSP的利用等情况来精确计算芯片的功耗。

图2所示是为该系统中Stratix II电源内核供电的原理图。

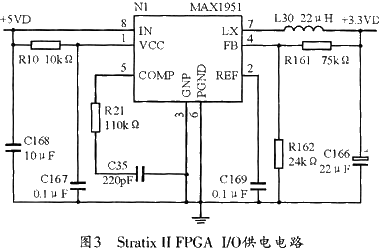

2.2 Stratix II FPGA的I/O端口供电电路

因Stratix II内核供电分为锁相环模拟电源和内核数字电源两种,其中锁相环所需电源要求纯净、稳定,所以在MAX1951输出的后端可用两个磁珠对模拟和数字电源进行隔离,并对PLL模拟电路再次进行滤波,同时在FPGA器件周围放置相应数量的0.1μF的引脚滤波电容。

Stratix II FPGA的I/O与PD的供电要求不怎么严格,所以可接成共电3.3VD,经估算,其最大工作电流为0.1A。因此,按照本文所提供的关系式可以很容易地得出其输入输出滤波网络的参数,图3所示是用MAX1951设计的Stratix II FPGA系统的I/O口供电电路。

到此为止,Stratix II FPGA供电系统设计完毕。

3 结束语

Stratix Il FPGA的高级架构特性结合Nios II嵌入处理器具有无与伦比的处理能力,能满足网络、电信、DSP应用、大容量存储和其它高带宽系统的需求。因此,本文基于MAX1951在StratiXII电源供电中的稳定性以及功率控制等方面的良好表现,可以推广到现代绝大多数低功耗器件的电源设计中去。

- HIN2xxE系列RS-232收发器的原理及应用(01-18)

- 什么是FSL总线(01-03)

- 满足FPGA电源设计需求的DC/DC转换器(02-15)

- 数字电源管理芯片ZL2105的性能及性能测试设计(06-02)

- Tensilica HiFi 2音频DSP支持RealAudio解码器(01-07)

- Silicon Labs扩充多脚数、触摸感应装置单片机产品线(02-05)