基于功耗限制的CMOS低曝声放大器最优化设计

时间:03-09

来源:电子设计应用

点击:

出端电感Lt与M2的漏极总电容C2谐振在工作频率时,则电压增益为:

因此,增大晶体管的跨导和电感的Q′L值能有效地提高增益。另外,源极负反馈电感Ls的取值对增益也有影响。一般可以采用增大静态电流和晶体管尺寸的方法增大跨导,但应考虑电路功耗的限制。本文设计的LNA采用的电感均为CMOS工艺的片内螺旋电感,Q′L值都不高,所以应选用Q′L值高的螺旋电感以提高增益。

2 模拟结果

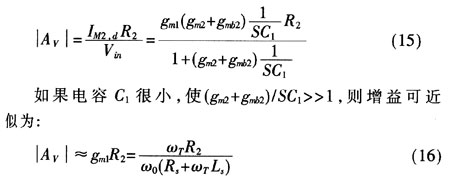

电路中所有元件取自Chater公司0.25μmCMOS RF工艺库,并全部集成在芯片内部。使用Cadence的Spec-tre进行了模拟分析。LNA的S参数如图3所示,由图可知,模拟显示该放大器的功耗为16mW,正向增益S21在2.4GHz频率时最大值为15dB,反射系数S11小于-23dB,S22小于-20dB。由此说明低噪声放大器实现了与输入、输出端口的良好匹配,并能取得较大的增益。噪声系数的频率响应如图4所示,NF在2.4GHz处取得最小值2.7dB。对线性度进行了模拟,LNA的1dB压缩点如图5所示,1dB压缩点为-10.5dBm。表1列出了低噪声放大器的模拟结果。

本文详细介绍了功耗限制条件下噪声最优化的低噪声放大器的设计方法,并采用0.251μmCMOS RF工艺设计了一种2.4GHz低噪声放大器。模拟结果表明,采用2.5V电源时,功耗为16mW,在2.4GHz工作频率下,正向增益S21可达15dB,反射参数S11小于-23dB,S22小于-20dB,噪声系数NF为2.7dB。

作者:徐跃

LNA 相关文章:

- 利用阻性负载增强LNA稳定性(中)(11-19)

- 稳定低噪声放大器中晶体管工作点的设计方法(下)(11-20)

- 利用阻性负载增强LNA稳定性(下)(11-19)

- 稳定低噪声放大器中晶体管工作点的设计方法(上)(11-19)

- 利用阻性负载增强LNA稳定性(上)(11-19)

- 使用前置放大器有助于提高测量质量(01-16)