迟滞电路(hysteresis circuit)又称施密特触发电路(schmitt trigger circuit)。因他能滤除干扰噪声而获得很广泛的运用。在一些应用场合中,特别在某些模/数转换电路中

[1],迟滞比较器作为抗干扰的比较器应用较多。为了获得更好的转换效果,需要较好地选择迟滞比较器正端输入的基准电压。而信号的未知为确定基准电压带来麻烦。本文设计的一种加入滤波器的迟滞比较器解决了这个问题。

1 迟滞比较器的设计

迟滞性是比较器的一种特性,他使比较器的输入阈值随输入(出)电平而改变。比较器实现的方法很多。他们都有不同形式的正反馈。最常见的即是由放大器接成正反馈组成。这类迟滞比较器由于方便的设计和放大器的标准生产成为主流。设计选用了最常见的由放大器正反馈的设计,如图1所示。

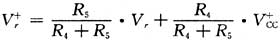

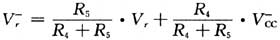

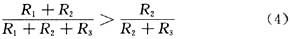

由米尔曼公式可得输入电压升高和降低时的基准电压如下式:

|

而电路能滤掉的噪声即迟滞性为: |

由上式可知,迟滞性由电源电压和R4,R5阻值决定。本设计中Vr的大小是变成的,因此正负基准电压也随Vr变化,为了达到自适应的目的希望基准电压对输入有好的跟随性同时减小输出端的影响。因此将R4取值得比R5要小一个数量级。 |

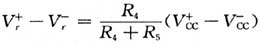

2 滤波器的设计 设计滤波器往往要考虑下列因素: (1)工作频率范围。 (2)参数变化的灵敏度及稳定度。 (3)实际元件的重量和大小。 (4)运算放大器的电压源。 2.1 滤波器的选择[2] 本设计是工作在低频的比较器。此时当信号频率是低频时可以考虑的方式有低通、带通或全通,同时还可选择一阶或多阶。在考虑此设计后,一阶滤波器在此设计中是较好的,且低通滤波器是相对比较简单的,所以设计选择低通滤波器。简单低通滤波器通常可由电容与电阻组成。本设计采用了电容与电阻并联接地的方式,最后的滤波器连同迟滞比较器设计如图2所示。 |

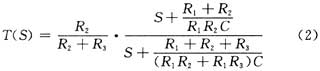

2.2 元件值的确定[3] 一阶的滤波器有公用的传输函数: |

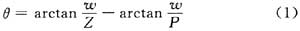

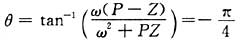

其中Z是T(S)的零点,P是极点,在S平面上,Z可能落在正实轴或负实轴上,而P永远落在负实轴上。其中K为正数时由函数T(S)的相位公式得: |

由图2得其传输函数标准形式为: |

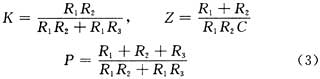

则: |

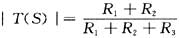

对于S,当S=jω=0时: |

当S=jω趋向无穷大∞时: |

由上式可知,电阻值可按设计的要求大概约束,如果需要其是低通滤波器则有关系式: |

当上式成立时,滤波器为低通。当R为正实数时与上式等价。同时需要S=0时|T(S)|接近1为约束条件。由以上条件可知R1的电阻最大,R3的电阻与其有可比性。在此取R1=10R3,R2的电阻比其低几个数量级。 下面进行相位约束条件的探讨: 将S=jω代入式(2)中有: |

计算相位的公式如下: |

由式(6)结合式(1)可得: |

要此电路在1 rad/s为处有45°的相位落差即要求: |

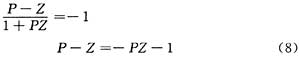

| 则有:

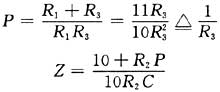

而结合式(3),(4),(5),因为R1=10R3,R2的电阻比其低几个数量级,则有: |

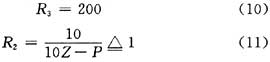

两式联立求解并取C=1,可得: |

根本式(7):当一个方程有两个未知数,可取得的某一个为定值。如果计算后是合理值,便能解决问题。选择P=0.005,由式(7)得Z=1,则: |

从以上的结果可以找出元件值[3]。由于Cnew= ,Rnew=kmRold,根据实际电路中元件值的需要,如果按kf=1来设计很难与实际电容大小匹配。在此令kf=1 000,km=420。得电路元件的实际值为:R1=840kΩ,R3=84kΩ,R2=420Ω,C=2.34μF。再将C的值标准化为2.2μF。对R4选择值为R3的1/10,即8.4kΩ,R5则确定为R4的20倍为170kΩ。 ,Rnew=kmRold,根据实际电路中元件值的需要,如果按kf=1来设计很难与实际电容大小匹配。在此令kf=1 000,km=420。得电路元件的实际值为:R1=840kΩ,R3=84kΩ,R2=420Ω,C=2.34μF。再将C的值标准化为2.2μF。对R4选择值为R3的1/10,即8.4kΩ,R5则确定为R4的20倍为170kΩ。 3 仿真和讨论 仿真在HSpice[5]下进行,设定其电源电压为2.3V,输入信号选择正弦信号。用HSpice的表示方法[6]为sin(1.2V 0.45V 1Hz)即直流偏置为1.2V,幅值为0.45V,频率为1Hz。其仿真波形如图3所示。 | | | | | | | | | | | | | | | | | | |