电源管理单元技术实现架构和未来趋势分析

电源管理 相关文章:

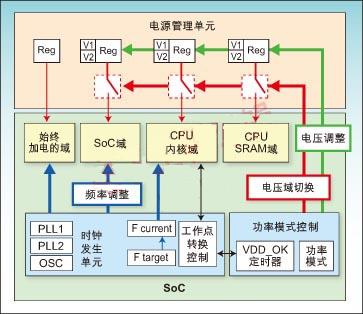

图1:SoC及其电源管理单元之间典型的互动,实现了电压域切换、电压调整与频率调整

动态电源控制

随着所谓动态电压与频率调整(DVFS)技术的引入,PMU及其供电的SoC之间的耦合将变得更加紧密。与电压岛方法相同,该技术在SoC中建立了多个时钟频率域,从而可以减小对芯片各部分的供电电压,动态电压与频率调整可根据系统处理器的活动情况,自动调节时钟频率与供电电压。这样就把电源管理与软件活动直接联系在一起。

DVFS的实现需要系统运行附加的软件来评估当前处理器的负载,并预测出在实时系统约束下完成这个处理负载所需时钟速度。这样就可以将时钟速度降低到适当的频率上,而供电电压也降低到能够维持这一时钟速度的水平。为了满足典型系统的实时约束,DVFS过程必须每间隔数毫秒被重复,或者当任务进度表或中断驱动的软件例程明显改变处理器负荷时就被重复。

DVFS的实现可以是开环,也可以是闭环过程(见图2)。开环DVFS中为目标系统确定了多种不同频率和电压工作点,系统被设置到最接近的工作点,能够确保所需处理性能。在实际应用中,不同工作点的数量一般限制为2或4个,每个工作点都必须保证相应处理器负荷下的性能,另外还要考虑到最糟情况下的工艺变动(由于工艺技术的变化而造成的系统性能波动)、IR压降(例如PCB走线造成的IR压降)以及温度效应。这些都意味着在相当多的时间里电源电压仍然会高于严格的需求指标。而由于功耗与电源电压的平方成正比,即使少量的电压超额也会有明显的效应。

闭环DVFS对系统的实际硅性能提供直接反馈,并考虑到了工艺变化及温度变化的影响,从而解决了这些问题。其中每个SoC中都包含了一个性能监控器,它在各个时间点测量给定电压上SoC的实际性能。然后,该性能监控器的输出向电源管理算法提供信息,以决定电压是该升高还是降低,从而将其保持在SoC最佳的功耗性能比范围中。

为了在片上性能监控器与PMU之间提供一个标准接口,美国国家半导体公司和ARM提出了他们联合开发的PowerWise接口(PWI),这是一个开放的工业标准。移动工业处理器接口(MIPI)联盟也强调了此类开放工业标准的重要性,他们正在致力于建立一个系统电源管理接口(SPMI)规范。

C050PMU工艺

与消费电子中的所有事物一样,PMU也不断迈向更高集成度,这不仅为了降低成本,也是为了减小物理尺寸,从而能为移动便携式设备中的其它功能腾出空间。因此最理想的方案应该是单芯片,以尽可能减少外围元件。

实现PMU对半导体工艺技术的要求包括:能集成可承载高达1A电流、能在正常运行和电池充电期间承受电池与充电器峰值电压的低导通电阻MOSFET;另外还应能集成低功耗的逻辑电路,用于控制切换与稳压功能。

飞利浦最新一代PMU采用该公司基于0.25um CMOS的C050PMU工艺。只需几个额外的掩膜步骤,额定3.3V的基线工艺就可提升至正常电池应用的5V(单锂离子电池,或三节镍镉或镍氢电池);如果PMU会在脉冲充电期间遭受感性电压毛刺,或者需要超出电池的正常电压(例如,驱动串接的背光照明LED),则可以达到20V。C050PMU工艺可为PMU以及开关转换器控制电路的实现提供足够的逻辑密度,另外还有一种工艺选项,可以在PMU中包含一次编程(OTP)非易失存储器,用于定义PMU的起动条件。而完全可重编程的EEPROM选项正在开发中。

飞利浦还有一个专门的PMU设计库与设计环境,可以用构建模块的方法快速建立PMU设计。库中的基本IP块包括带隙电压基准、输出能力从数毫安至数百毫安的低压降线性稳压器(LDO)、可提供高达1A电流且效率超过90%的DC/DC转换器块,以及PMU控制状态机。LDO可以针对多种性能参数作优化,例如,敏感电路(如射频收发器)需要的低输出噪声电源。其它库元件包括上电复位电路、时钟振荡器、低功耗实时时钟/日历电路,以及I2C/SPI串行总线接口。

使用C050PMU工艺的设计者还可以使用该公司几乎所有0.25um混合信号与模拟IP块,包括先进的音频编解码器、耳机与音箱放大器、麦克风放大器、滤波器、ADC和DAC等。这对系统设计者非常重要,因为他们会希望在同一芯片中集成PMU和混合信号/模拟IP,例如,在手机或音乐播放机中将PMU与模拟基带功能集成在一起。

未来发展趋势

除了DVFS所需的片上性能监控器以外,未来还将有越来越多的电源管理功能移至芯片上。例如在手机市场上,越来越多的附加功能采用SoC来实现,现在已经有种需求是将每片SoC直接连接在公共的准稳压电压轨上,一般在1.8V左右。这样就要求DVFS所需的可编程稳压器移至芯片上,而不是集成到一个独立的PMU中。鉴于这一因素,飞利浦公司已经开始迁移很多与PMU相关的IP,即从当前的0.25um C050PMU工艺直接转到深亚微米CMOS工艺技术。

在电池与这些SoC之间,只需要用一个高效率的DC/DC转换器生成公共电源。现有的DC/DC转换器已经能够在所有负载条件下提供高于90%的效率。但是,要将它们做到小型化还有相当多的工作要做。

现有的开关模式转换器最高工作频率大约是2MHz,因此仍然要使用体积相对较大的电感器。正在开发中的新型转换器工作频率在10MHz以上,它可以使电感器体积减小到可以集成的程度,即使不是放在片上,也可以作为系统级封装(SiP)PMU方案的一部分。还有一种很快就可能集成到PMU中的元件,即基准电压和LDO的输出去耦电容。作为无源集成工具箱中的一部分,飞利浦已经拥有一种工艺技术,能在硅片上实现高达230nF/mm2的电容密度,可以用于SiP方案的集成。

另外不要忘记,移动设备的液晶屏和背光照明功耗通常要占到总体的一半。新型显示技术与相应的PMU结合,也能在降低总体功耗方面扮演相当重要的角色。

作者:Henk Derks

Ronald van Cleef

Reinier van der Lee

飞利浦半导体公司