改善电源负载瞬态响应性能的设计方法

时间:01-09

来源:国际电子商情

点击:

电子电路一般都需要一个即使在负载电流发生瞬变时,输出电压也能维持在特定容差范围内的电压源,以确保电路的正常工作。设计工程师必须在理解瞬态响应原理的基础上,利用正确的设计思路才能以较低的成本改善电源的瞬态响应性能。

瞬态定义为"仅维持一段短暂时间的事物"。但是,随着微处理器工作速度和电流需求量的提高,当负载电流发生瞬态变化时,稳压器在指定范围内保持输出电压的能力成为一个广泛存在的困扰。典型CPU芯片的电源规范要求,即使负载电流在几百纳秒内发生20或30A的变化,供电电压仍然要保持稳定,要实现这个性能指标绝非易事。

瞬态响应可能是电子电压调节里最难理解的概念之一。在过去曾有一个曾经有人做出一个完全错误的陈述:"我们新推出的稳压器速度之快甚至可以使你不再需要电容。"事实相反,当负载瞬变时(不管这个稳压器有多快),你始终需要电容。

总之,为了掌握在哪里投入成本才能提高系统性能和在不牺牲瞬态的情况下怎样节省成本,你需要理解瞬态响应是什么以及它的工作原理。

电压调节

几乎所有的电子电路都需要一个稳定的电压源,它维持在特定容差范围内,以确保正确运行(典型的CPU电路只允许电压源与额定电压的最大偏离不超过±3%)。该固定电压由某些种类的稳压器提供。通过电阻分压器自动检测输出电压,误差放大器不断调整电流源从而维持输出电压稳定在额定电压上。

稳压器必须能够在负载电流需求量从零上升到满负荷(大约为20A或更多)时,保持输出电压恒定。当负载电流需求量缓慢变化时很容易做到这一点,但是,如果负载电流"阶跃"足够快的话,稳压器将无法提供完全稳定的输出电压。

理解负载瞬变的关键点:

1. 稳压器担当驱动负载的压控电流源(通过输出端的电压反馈对电流源进行调节)的角色。稳压器的电流源永远不可能在零时间内作出变化,因此可以得出结论,如果我们使负载电流的变化速度超过稳压器的响应速度,输出电压将会发生变化。

2. 在稳压器的控制环路对负载变化进行调整的时间间隔,对负载电流变化(在先前的稳态值和新的负载电流之间)进行供给的唯一来源是输出电容。因此,不管你喜欢与否,我们都必须加入输出电容以试图在负载瞬变时维持输出电压恒定。系统规范规定了所必须使用电容的大小和种类。

3. 稳压器的速度越快越好。稳压器的控制环路响应速度越快,在环路纠正瞬变前输出电容上的电压变化就越小。因此可以看出,更快的稳压器意味着在获得同等"负载调节容差范围"的情况下能够采用更小的输出电容(节省成本)。

负载瞬变

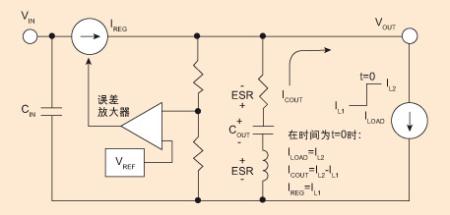

为了了解负载瞬变如何发生,下面用一个例子来进行分析。本例中,当负载电流需求量在几乎零时间内从IL1变化到更大值(IL2)时发生了负载瞬变。在瞬变之前,稳压器处于稳态运行,这时IREG= IL1,并且输出电容没有向外部电路输出电流。

稳压器的电流源(IREG)不能立即发生变化,因此在"t = 0+"时刻(也就是负载电流增加到IL2的瞬间),IREG = IL1。通过简单节点分析得出,此时电流源需要输出电容:

ICOUT=IL2-IL1

COUT将继续提供电流直到控制环路把IREG提高到IL2为止。在COUT必须提供电流期间,随着电容放电,它两侧的电压将会降低。电容的内部寄生等效串联电阻(ESR)和等效串联电感(ESL)同样也会使COUT两侧的电压降低,如图1所示。

瞬态定义为"仅维持一段短暂时间的事物"。但是,随着微处理器工作速度和电流需求量的提高,当负载电流发生瞬态变化时,稳压器在指定范围内保持输出电压的能力成为一个广泛存在的困扰。典型CPU芯片的电源规范要求,即使负载电流在几百纳秒内发生20或30A的变化,供电电压仍然要保持稳定,要实现这个性能指标绝非易事。

瞬态响应可能是电子电压调节里最难理解的概念之一。在过去曾有一个曾经有人做出一个完全错误的陈述:"我们新推出的稳压器速度之快甚至可以使你不再需要电容。"事实相反,当负载瞬变时(不管这个稳压器有多快),你始终需要电容。

总之,为了掌握在哪里投入成本才能提高系统性能和在不牺牲瞬态的情况下怎样节省成本,你需要理解瞬态响应是什么以及它的工作原理。

电压调节

几乎所有的电子电路都需要一个稳定的电压源,它维持在特定容差范围内,以确保正确运行(典型的CPU电路只允许电压源与额定电压的最大偏离不超过±3%)。该固定电压由某些种类的稳压器提供。通过电阻分压器自动检测输出电压,误差放大器不断调整电流源从而维持输出电压稳定在额定电压上。

稳压器必须能够在负载电流需求量从零上升到满负荷(大约为20A或更多)时,保持输出电压恒定。当负载电流需求量缓慢变化时很容易做到这一点,但是,如果负载电流"阶跃"足够快的话,稳压器将无法提供完全稳定的输出电压。

理解负载瞬变的关键点:

1. 稳压器担当驱动负载的压控电流源(通过输出端的电压反馈对电流源进行调节)的角色。稳压器的电流源永远不可能在零时间内作出变化,因此可以得出结论,如果我们使负载电流的变化速度超过稳压器的响应速度,输出电压将会发生变化。

2. 在稳压器的控制环路对负载变化进行调整的时间间隔,对负载电流变化(在先前的稳态值和新的负载电流之间)进行供给的唯一来源是输出电容。因此,不管你喜欢与否,我们都必须加入输出电容以试图在负载瞬变时维持输出电压恒定。系统规范规定了所必须使用电容的大小和种类。

3. 稳压器的速度越快越好。稳压器的控制环路响应速度越快,在环路纠正瞬变前输出电容上的电压变化就越小。因此可以看出,更快的稳压器意味着在获得同等"负载调节容差范围"的情况下能够采用更小的输出电容(节省成本)。

负载瞬变

为了了解负载瞬变如何发生,下面用一个例子来进行分析。本例中,当负载电流需求量在几乎零时间内从IL1变化到更大值(IL2)时发生了负载瞬变。在瞬变之前,稳压器处于稳态运行,这时IREG= IL1,并且输出电容没有向外部电路输出电流。

稳压器的电流源(IREG)不能立即发生变化,因此在"t = 0+"时刻(也就是负载电流增加到IL2的瞬间),IREG = IL1。通过简单节点分析得出,此时电流源需要输出电容:

ICOUT=IL2-IL1

COUT将继续提供电流直到控制环路把IREG提高到IL2为止。在COUT必须提供电流期间,随着电容放电,它两侧的电压将会降低。电容的内部寄生等效串联电阻(ESR)和等效串联电感(ESL)同样也会使COUT两侧的电压降低,如图1所示。

图1:电流增加负载瞬变的发生 输出电压瞬态响应 所有的电容都含有ESR和ESL,二者都会对瞬态响应产生明显的影响。在一个增加的电流负载瞬变过程中看到的输出电压与图2中显示的类似。

|

- 在电源中起到廉价运放作用的并联稳压器 (11-30)

- 五类主要线性稳压器的优缺点及其应用领域分析(01-09)

- 单片式降压型稳压器为DSP提供片内电源排序(01-09)

- 用于固定开启时间稳压器的低ESR稳定技术(01-10)

- 构成大功率反相-5V电源的降压型稳压器的设计(01-22)

- 三端并联稳压器的隐藏应用(06-20)