低频正弦信号发生器的设计

个8 位的数模转换器, 形成正弦脉冲波, 经过一个低通滤波器平滑波形后输出。下面分别介绍这4 部分的组成和原理。

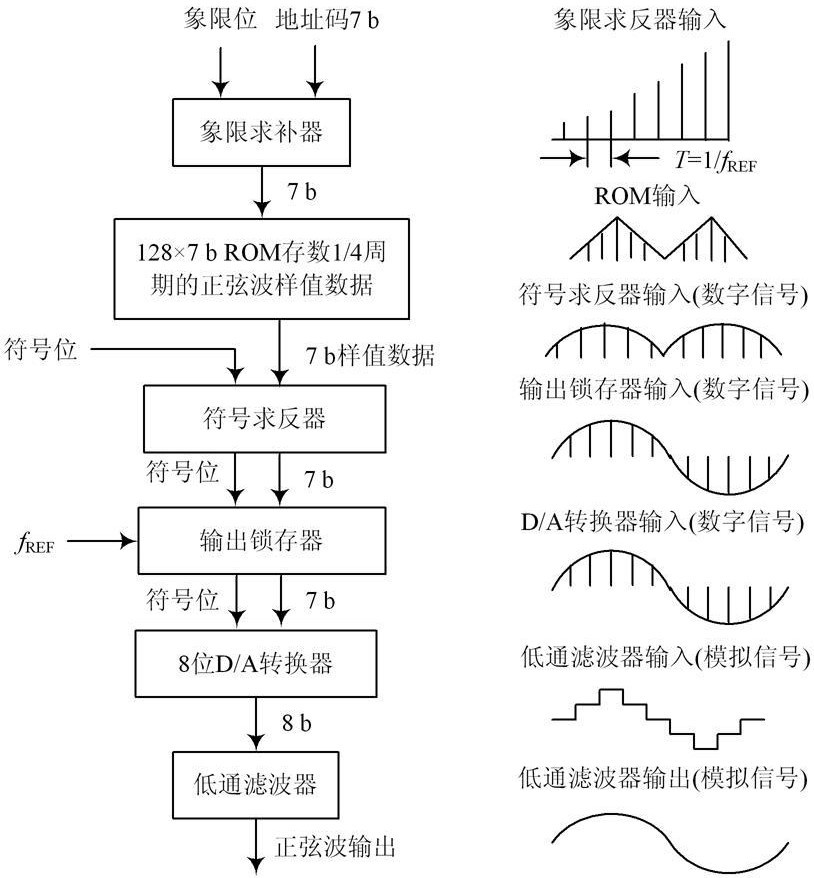

图1 原理框图

2. 1 相位累加器

相位累加器如图2 所示, 它是DDS 的核心部件, 由加法器和相位锁存器构成。每来一个时钟脉冲, 相位寄存器的输出就增加一个步长的相位增量值, 加法器将频率控制数据与累加寄存器输出的累加相位数据相加, 把相加结果送至累加寄存器的数据输入端。相位累加器进入线性相位累加, 至满量程时产生一次计数溢出, 这个溢出频率即为DDS 的输出频率。加法器A 组的低16 位( A15 ~ A0 ) 接串行输入接口电路的16 位锁存器输出, 高5 位( A20 ~ A16 ) 全部接地。B 组( B20 ~ B0 ) 作为后端锁存器的反馈输入。

图2 相位累加器

2. 2 正弦波发生器

正弦波发生器如图3 所示。由相位累加器送来的低7 位地址码和第8 位( 象限位) 先送到象限求补器。

象限位为0 时, 象限求补器保持地址码不变; 象限位为1 时, 它对地址码进行模128 求补。在1 个T OUT 内, 生成4 个的TO UT / 4 位地址码。这些地址码被送到ROM用于搜索对应相位点的正弦波样值, 以获得2 个半波的正弦波样值数据, 连同相位累加器的最高位一起送到符号求反器。这样使得第一个半波不变, 第二个半波被倒相, 从而生成一个周期的完整正弦波样值数据。将相位寄存器的输出与相位控制字相加得到的数据作为一个地址对正弦查询表进行寻址, 查询表把输入的地址相位信息映射成正弦波幅度信号, 驱动DAC 做D/ A 转换,输出模拟信号; 低通滤波器平滑, 输出频谱纯净的正弦波信号。

由DDS 的基本原理可以知道, 输出的正弦信号将有可能出现误差。对于不同的参考时钟, 将产生不同程度的频率误差, 表1 例举了ML2035 在常见的晶振下的频率控制字和频率误差情况。

图3 正弦信号发生器

表1 在常见的晶振下的频率控制字和误差

3 低频信号发生器的设计

输出的正弦信号的频率可以由16 b 的串行比特字控制, 广泛地应用在输出正弦波要求高的领域。

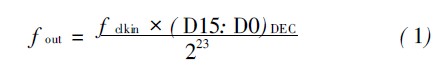

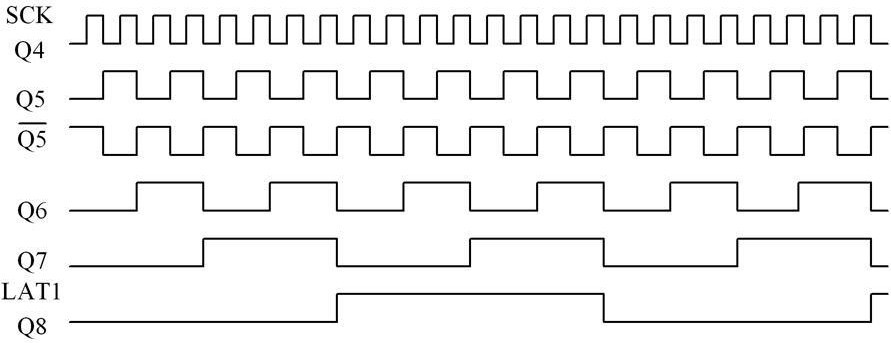

频率设置值是通过SID 脚串行输入的。数据在SCK 的上升沿移入。当16 b 数据都进入移位寄存器后, 在LAT 1 的下降沿锁存。由于ML2035 的控制字是16 b, 因此据DDS 的原理可以得出ML2035 的输出频率关系式为:

相应地,ML2035 的频率分辨率为:

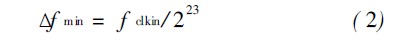

产生100 Hz 的正弦信号, 系统所用晶振选取6. 553 6 MHz, 通过输出的频率关系式( 1) 可以计算出16 b 的控制字为0000000010000000, 则由74LS20 产生16 b 的控制字输入到ML2035 的SID 端, 控制输出频率为100 Hz 的正弦信号。通过ML2035 的LAT 1 端在时钟的下降沿将频率控制字锁入16 b 数据锁存器中。正弦信号发生器如图4 所示。

图4 100 H z 正弦信号发生器

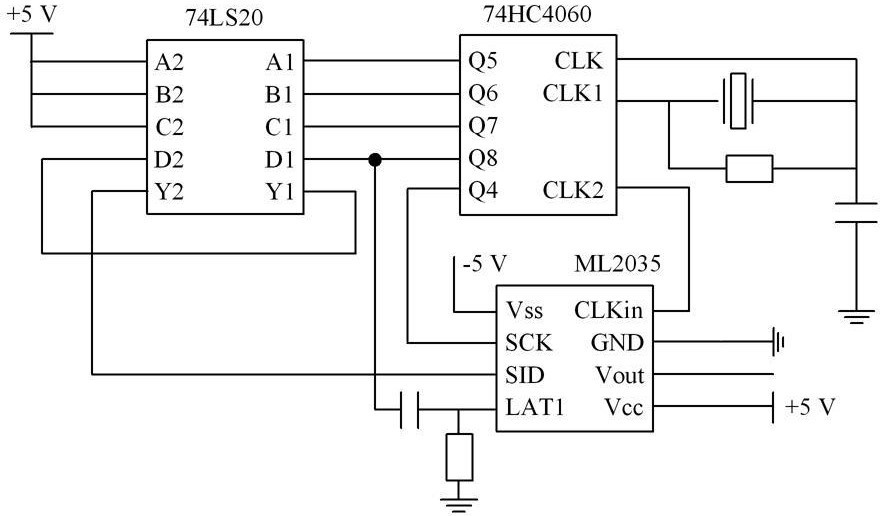

输出的脉冲时序图如图5 所示。

图5 脉冲时序图

则产生100 Hz 正弦波信号的控制字应由f out = Q5.Q6.Q7.Q8 得出。

4 结语

由于能够在外围器件较少的情况下, 产生精度和稳定度较高的正弦信号。因此可以应用ML2035 设计出频率在0~ 25 kHz 的高稳定的、高精度的正弦波形。由ML2035 的工作原理, 设计了100 Hz 的正弦信号发生器, 实验证明该信号发生器具有较高的稳定度和精度。

- 基于DSP的低频感应通信系统设计(10-16)

- 2DPSK低频感应通信系统MATLAB仿真(10-18)

- 一种新型的正弦信号发生器的设计与实现(04-23)