基于DDS技术的多路同步信号源的设计

。

2.3 相位累加器的设计

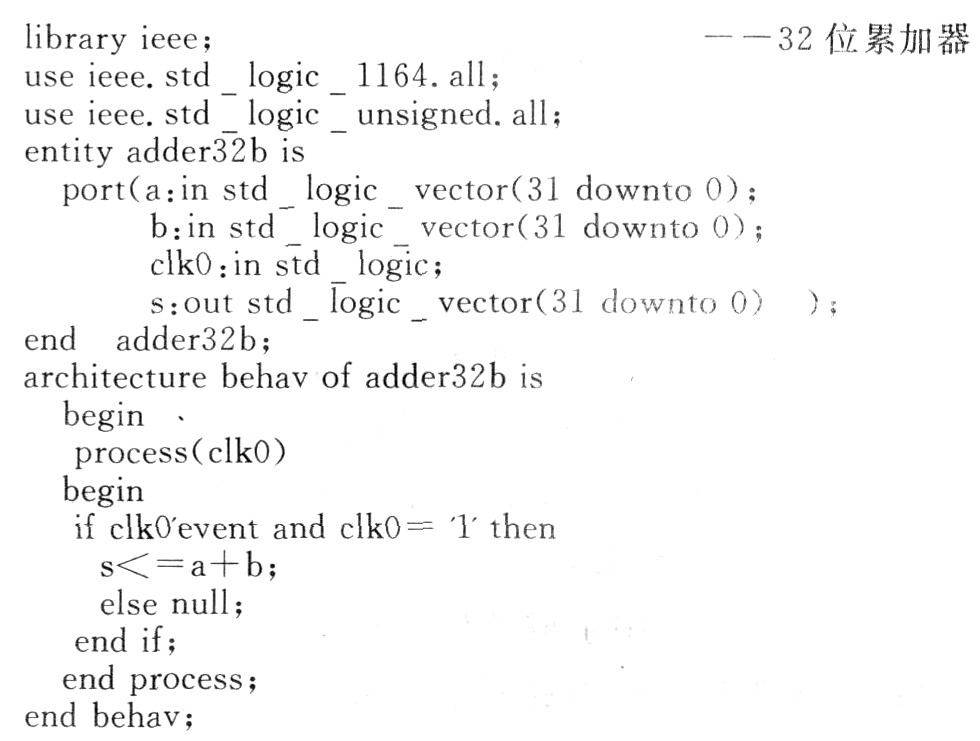

相位累加器是DDS设计的核心部件。本设计相位累加器由32位加法器与32位寄存器级联构成。累加器将加法器在上一个时钟作用后所产生的相位数据反馈到加法器的输入端;使加法器在下一个时钟作用下继续与频率控制字(K)进行相加,实现相位累加,当相位累加器累加结果等于或大于232时就会产生一次溢出,回到初始状态,完成一个周期性的波形输出。本设计累加器用VHDL语言[quartus6.0]设计实现如下:

32位累加器模块实现:

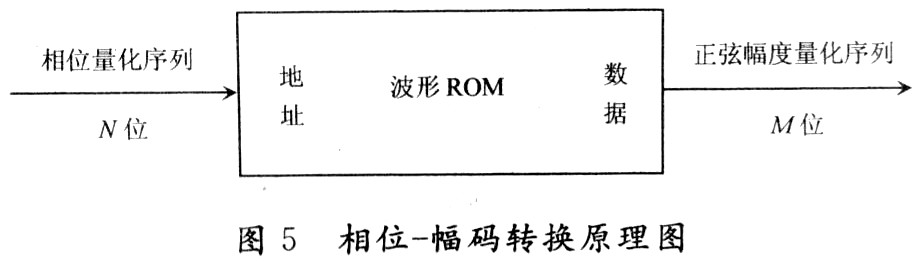

2.4 波形存储器的设计

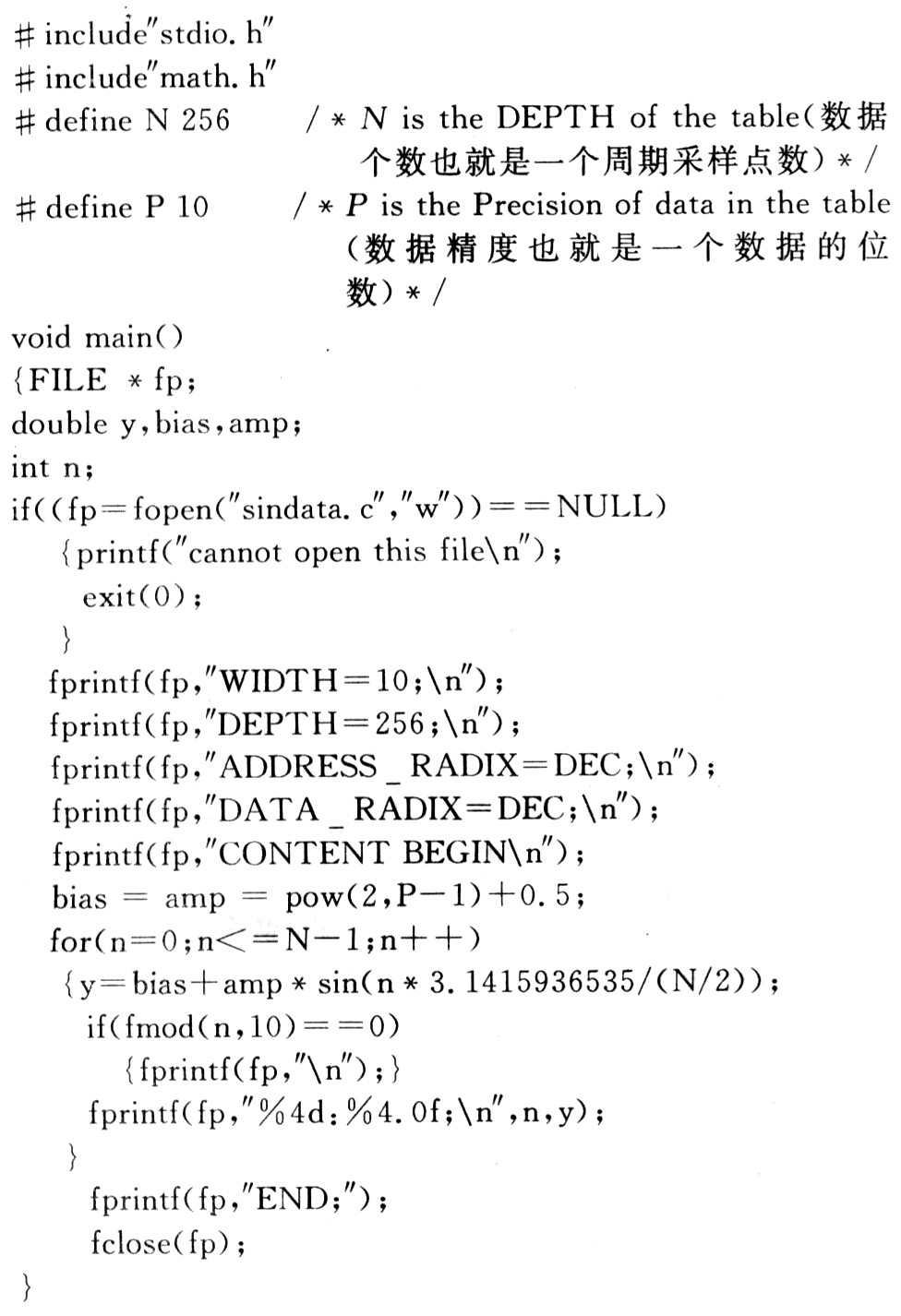

用相位累加器输出的数据作为波形存储器的取样地址,进行波形的相位一幅码转换,即可在给定的时间上确定输出的波形的抽样幅码。本设计利用FPGA资源,构造一个10位的ROM进行数据的存储和转换。

ROM可利用Quartus的插件管理程序Megawiz-ard plug-in manager容易获得,这里给出正弦波形数据生成的C程序,来生成ROM存储的数据。要想生成其他波形的数据,只需要简单修改其中的波形表达式即可。

3 仿真与调试

本设计在Quartus Ⅱ中进行分析和综合后,得到该相位可调多输出DDS的结构如图6所示。

在Quartus Ⅱ中,输入控制信号:Fo=100 MHz,fword=50,pword=35,进行仿真,其仿真结果如图7所示。在Quartus中生成的仿真数据经过验证完全正确,得到了同频和可调相的三个正弦波的幅值数据序列,完全满足设计要求。

4 结 语

本设计运用VHDL硬件编程语言和DDS技术,结合FPGA高速器件,实现了多路信号的同步输出,很好地解决了要求信号之间同频率可调,相位连续可调的问题,且具有易于程控、相位连续、输出频率稳定度高、分辨率高等优点,并且采用一个FPGA块就解决了传统上需要三个DDS才能解决的问题,也大大降低了设计成本。

- 严酷的汽车环境要求高性能电源转换(08-17)

- 管理多电压轨系统让数字电源管理变得简单(08-17)

- 电源监视器LTC4151对汽车应用的解决方案(08-10)

- 具USB OTG和过压保护的紧凑型电源管理器(08-17)

- 适合有源天线系统并内置保护和诊断功能的坚固、低噪声、稳定型电源(08-16)

- 并联充电器系统可从以往不可用的低电流电源收集功率(08-23)