降低dc/dc开关式转换器的接地噪声设计

时间:08-17

来源:3721RD

点击:

直到辐射出去或耗散在阻性元件上。

地噪声振荡的峰值电压和持续时间都是问题。峰值电压在结点VGB测量,它是LX结点电压变化、寄生的降压电感器电容以及附加寄生走线电容的函数。一个大的寄生降压电感器的电容会存储更多能量,因此采用一个较小值是一个比较好的方案。选择了降压电感器的值以及额定电流后,要选择有最大自谐振频率的电感,以限制CL的容量。电感器的自谐振频率表示为1/[2π√(LBUCKCL)]。自谐振频率加倍可降低寄生的电感器电容,因而地噪声能量可降低至其四分之一。

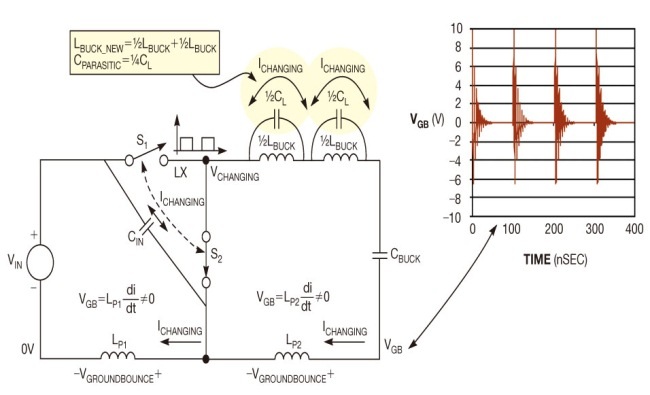

当性能优先于成本考虑时,用两只串联电感替换图5中的单只降压电感,每只电感的值是降压电感值的一半,而总电感值保持不变(图6)。对于制造厂的系列电感产品,寄生电容通常与额定电感值成正比,因此半值电感的寄生电容也只有一半。采用串联电感时,它们的电感值相加,而寄生电容值则是倒数值的和的倒数,从而降低了总的寄生电容。对于两个串联的半值电感,总电感值为LbuckNEW ,而总寄生电容将降低至降压电感器电容的四分之一。这样,降低的寄生电感就减少了地的弹跳。

图6,两个串联电感有相同的电感值,但寄生电容只有四分之一,泵出电荷及因此造成的地弹跳都得到减少。

通过研究各种模型,我们了解了地噪声的两个主要来源和机制,这两种地噪声在dc/dc开关转换器中无处不在,工程师可以在设计的早期阶段、元件选择以及布局时尽量降低这些效应,就能减少以后生产中的麻烦并避免从头设计。

- 为EMI敏感和高速SERDES系统供电(08-17)

- 高可靠DC/DC变换器模块设计(09-15)

- DC/DC转换器的发热问题缘由(10-30)

- 一种CMOS绿色模式AC/DC控制器振荡器电路(09-16)

- 凌力尔特大功率多相同步升压型DC/DC控制器LTC3787(10-15)

- 电动 / 混合电动汽车电池管理系统的可靠性(11-09)