变频器惯性输出技术

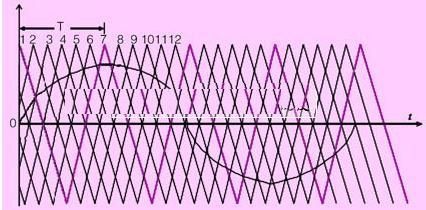

相位移载波技术的基本原理是使用几个1.2khz三角载波信号和一个正弦参考信号(每相) 比较,产生spwm信号。将三角载波进行合适的移相,可以消除特定次数的谐波。以a相为例,正弦调制波和三角载波如图3所示。六级功率单元使用的正弦调制波的幅值和相位相同,而每级功率单元的三角载波形状相同相位不同,各载波间相角依次移动2π/6即60°,这样就可以有效抑制输出电压和电流变化率。h桥单元左右桥臂的调制波相位相反,有助于提高整个系统的等效载波比。试验已证明n级单元串联时的等效载波频率为三角载波的频率的2n倍,并且在该种方式控制下的直流电压利用率高。

图3 相位移载波调制原理图

目前所使用的变频器一般将上述比较过程放在cpu中完成,当cpu遇到干扰复位或程序出错的时候,变频器将停止输出。由fpga来完成三角波和正弦波的比较过程将很好的解决这个问题,利用cpu的强大计算能力实时计算参与比较的正弦波,利用fpga高速度的时钟精确产生移相三角波,然后在fpga中进行比较输出。

fpga脉冲发生器及惯性输出原理#e#4 fpga脉冲发生器及惯性输出原理

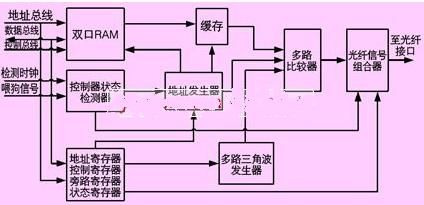

由fpga实现相位移载波spwm调制的结构框图如图4所示。fpga与cpu的接口由数据总线、地址总线和控制总线实现,cpu上电后首先对fpga的控制寄存器进行初始化,设置spwm的输出周期,各路三角波的初始相位和幅值。地址发生器根据周期寄存器的值产生ram读取地址,输出数据进入缓存。在每个三角波的谷值处给cpu一个中断,通知cpu更新数据,在每个三角波的峰值处从ram中读取数据进入缓存。cpu每次更新数据的同时也更新地址寄存器,指明当前输出数据的地址长度,此地址长度决定了变频器输出的频率。多路比较器实时将缓存数据与对应三角波进行比较产生spwm波形,光纤信号组合器将每一个功率单元所需信号即左臂信号、右臂信号、闭锁信号、旁路信号组合编码成一路串行信号送入光接口。

图4 fpga实现变频器惯性输出结构图

在fpga内部实现了一个看门狗(控制器状态检测器)对cpu进行监视,cpu在正常工作时,在每ms之内必须给fpga一个喂狗信号,当检测器在2ms没有检测到此信号变化则给地址发生器一个信号,地址发生器则根据当前的地址寄存器产生地址从双口ram中读取数据,从而实现cpu死机时变频器输出的相位和频率能够继续,即具有惯性输出功能。fpga实现惯性输出时,状态寄存器保存当前输出频率值和故障标志,以供cpu复位之后读取。

5 verilog设计与仿真

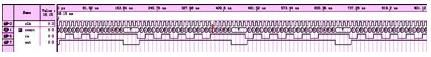

根据图4的结构框图应用verilog语言进行设计,选用lattice的xp3系列fpga进行设计,与传统的基于sram的fpga不同,latticexp3器件不需要外接引导存储器,因此能提供单芯片的解决方案,从而减少了电路板面积,并简化了系统制造过程。以控制状态检测器为例,当fpga在一段时间内检测到cpu的喂狗信号没有改变时,给出cpu异常信号,改变地址控制器的输出策略。其仿真图形如图5所示。

图5 cpu状态检测器仿真时序图

- 变频器在高速公路上的应用(06-29)

- 变频器对电机影响的解决方法(08-10)

- 变频器应用中的发热噪声谐波问题及应对措施(09-05)

- 风光高压变频器的电快速脉冲群干扰特点及抑制方法(11-15)

- 高压变频器电动机保护配置(11-26)

- 高压变频器在鼓风机中的应用(12-12)