保证嵌入式系统程序完整性的技术设计方案

门提供调用可信计算机中TCM密钥体系,让TCM、可信计算机与人的身份结合,构建完整可信计算信任链的吉大正元公司,则利用PKI/PMI技术,推出了可信接入安全支撑平台,保证不同网络可安全地接入整个体系。

虽然在PC领域,通过各机构和企业的努力,可信计算技术已经得到了一定程度的发展,但是在嵌入式系统领域,我国无论在规范还是在实际应用上,还是处于发展不足的状态。而基于嵌入式系统对于资源的敏感性,能源的紧缺性,功能的专业性等特点,生搬硬套过往的"大而全"的可信计算规范的服务显然是不合适。同时,目前市场上通用的TPM芯片大部分是通过与CPU的LPC引脚连接提供相关的加密验证服务。个人PC市场的处理器少厂商的垄断局面与嵌入式系统芯片市场百花齐放的情况不同,这也决定了现有的TPM芯片不能满足各种各样的传输接口需求。因此,一种基于嵌入式系统特性的安全保证技术实现方案的实现就显得非常必要。

2 系统建设总体原则

2.1 建设目标

本项目目的在于,基于目前现有的嵌入式部件的安全功能(Spartan-3A的Device DNA和中兴TCM芯片),提供一个保证嵌入式系统程序完整性的设计方案。于此同时,参照可信计算规范标准,为嵌入式系统打造一个可信根,为之后的可信链的建立及嵌入式可信平台的构造提供必要的条件。最终满足国内嵌入式系统安全需求,并为我国嵌入式系统可信技术独立自主发展提供支持。

2.2 建设原则

1、可扩展性原则:嵌入式系统本身就是一个被要求具备可扩展性的系统。其任务多变性,外设可裁剪性等原则也决定了本次设计应该具有与之匹配的特性。在保证核心,基本的完整性保证服务功能后,应该支持用户根据自身需要定制不同的,更复杂的安全性服务,即为今后系统应用的扩展和系统升级提供必要的接口。

2、安全性原则:由于设计中任何部件的安全性缺陷以及运行步骤上的漏洞都会导致系统被破坏的可能,所以本方案的安全性必须通过可信计算规范中可信链的建立过程进行论证。从而构造一个牢固的安全根基。

3、兼容性原则:基于嵌入式芯片厂商众多,使用的架构也不尽相同。因此本嵌入式系统程序完整性保证设计方案应该尽量做到只经过有限的修改甚至无需进行修改,即可应用到大部分主流的嵌入式系统之中。保证本设计的通用性。

3 项目研制内容

本项目对嵌入式系统完整性保证技术中的加密算法实现,系统部件身份识别,系统运行效率等关键技术进行了综合、深入的研究。

3.1 系统设计框架

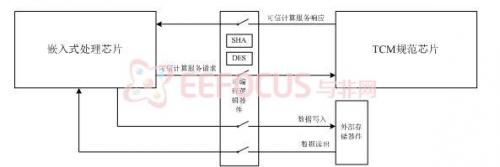

整个嵌入式系统设计总体结构图如下图所示,主要有主处理芯片、提供数据验证功能的可编程逻辑器件(FPGA)、提供TCM规范服务的TCM芯片以及外部存储器件。本系统运行与两种模式下:1、主要由FPGA与PC进行数据交互的配置模式。2嵌入式处理芯片,FPGA,TCM芯片协同工作的运行模式。

配置模式下,FPGA读出内部Device DNA,输出到PC端。之后扫描外部存储设备(如flash)制定地址区间的内容(一般为boot loader),进行SHA-1运算,产生数据摘要,输出到PC端。Device DNA会作为DES算法的密钥对上面提到的数据摘要进行加密,Device DNA与加密值会通过固件程序保存在TCM芯片的可信存储区域内。

运行模式下,主处理芯片通过FPGA产生的时钟信号进行工作。系统上电后,FPGA并不马上对主处理芯片提供时钟,而是先进行完整性验证工作:1、装载Device DNA,提供给内部DES运算部件作为密钥使用。2、请求TCM芯片发送32位随机数,此随机数将会被DES算法加密后送到FPGA,FPGA的DES部件对其进行解密后,进行存储。3、FPGA读取flash制定区域的内容,并进行SHA-1运算,产生160位数据摘要。4、160位数据摘要被分为5组,每组32位。每组与此前接收到的32位随机数组成64位数据,进行DES加密后,送到TCM芯片进行校验。5、TCM芯片接收到5组数据后进行解密。首先校验随机数部分是否与之前发出的一致,若一致,则继续校验数据摘要部分数据与之前在配置模式下写入的理想值是否一致。对比结果存放于特定内存位置。6、FPGA为主处理芯片提供时钟,并接通主处理芯片与外部存储器与TCM的数据通路。用户可以通过相关的接口读取对比值,判断系统是否被修改。

嵌入式完整性保证方案框架

3.2 安全性分析

硬件安全性: Spartan-3A,全部硬件逻辑固化在芯片内部,不可读取。TCM:通过国家商密办检验,不可读取。Boot Loader完整性:FPGA将依次读取Boot Loader的内容,并计算Hash值。对Boot ROM的任何篡改都将改变Hash值。从而导致验证不通过。

以下是几种可预见的攻击方式:1、在已知Boot loader的内容的前

- 在采用FPGA设计DSP系统中仿真的重要性 (06-21)

- 基于 DSP Builder的FIR滤波器的设计与实现(06-21)

- 基于FPGA的快速并行FFT及其在空间太阳望远镜图像锁定系统中的应用(06-21)

- 3DES算法的FPGA高速实现(06-21)

- 用FPGA实现FFT算法(06-21)

- FPGA的DSP性能揭秘(06-16)