ARM存储器之:协处理器CP15

式及含义如表15.8所示。

表15.8 类型标识符寄存器控制字段bit[8:6]含义

| 编 码 | M=0时的含义 | M=1时的含义 |

| 0b000 | 0.5KB | 0.75KB |

| 0b001 | 1KB | 1.5KB |

| 0b010 | 2KB | 3KB |

| 0b011 | 4KB | 6KB |

续表

| 编 码 | M=0时的含义 | M=1时的含义 |

| 0b100 | 8KB | 12KB |

| 0b101 | 16KB | 24KB |

| 0b110 | 32KB | 48KB |

| 0b111 | 64KB | 96KB |

bit[1:0]:定义Cache的块大小,其编码格式及含义如表15.9所示。

表15.9 类型标识符寄存器控制字段bit[1:0]含义

| 编 码 | Cache块大小 |

| 0b00 | 2个字(8字节) |

| 0b01 | 4个字(16字节) |

| 0b10 | 8个字(32字节) |

| 0b11 | 16个字(64字节) |

bit[5:3]:定义了Cache的相联属性,其编码格式及含义如表15.10所示。

表15.10 类型标识符寄存器控制字段bit[5:3]含义

| 编 码 | M=0时的含义 | M=1时的含义 |

| 0b000 | 1路相联 (直接映射) | 没有Cache |

| 0b001 | 2路相联 | 3路相联 |

| 0b010 | 4路相联 | 6路相联 |

| 0b011 | 8路相联 | 12路相联 |

| 0b100 | 16路相联 | 24路相联 |

| 0b101 | 32路相联 | 48路相联 |

| 0b110 | 64路相联 | 96路相联 |

| 0b111 | 128路相联 | 192路相联 |

15.1.4 寄存器c1

CP15中的寄存器c1包括以下控制功能:

· 禁止/使能MMU以及其他与存储系统有关的功能;

· 配置存储系统以及ARM处理器中相关的工作。

| | 注意 | 在寄存器c1中包含了一些没有使用的位,这些位在将来可能被扩展其他功能时使用。因此为了编写代码在将来更高版本的ARM处理器中仍可以使用,在修改寄存器c1中的位时应该使用"读取-修改特定位-写入"的操作序列。 |

当对寄存器c1进行读操作时,指令中CRm和opcode2的值将被处理器忽略,所以要人工将其置位为0。

例15.2用MRC/MCR指令将协处理器寄存器c1的值进行读取和写入。

【例15.2】

MRC P15,0,r0,c1,0,0 ;将寄存器c1的值读取到ARM寄存器r0中

MCR P15,0,r0,c1,0,0 ;将ARM寄存器r0的值写入寄存器c1

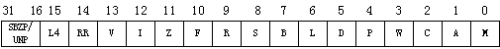

图15.7显示了寄存器c1的编码格式。

图15.7 寄存器c1编码格式

寄存器c1各控制字段的含义如表15.11所示。

表15.11 寄存器c1中各控制位字段的含义

| C1中的控制位 | 含 义 |

| M(bit[0]) | 禁止/使能MMU或者MPU 0:禁止MMU或者MPU 1:使能MMU或者MPU 如果系统中没有MMU或者MPU,读取时该位返回0,写入时忽略 |

| A(bit[1]) | 对于可以选择是否支持内存访问时地址对齐检查的系统,本位禁止/使能地址对齐检查功能 0:禁止地址对齐检查功能 1:使能地址对齐检查功能 对寄存器进行写操作时,忽略该位 |

| C(bit[2]) | 当数据Cache和指令Cache分开时,本控制位禁止/使能数据Cache。 当数据Cache和指令Cache统一时,该控制位禁止/使能整个Cache 0:禁止Cache 1:使能Cache 如果系统中不含Cache,读取时该位返回0,写入时忽略 当系统中Cache不能禁止时,读取返回1,写入时忽略 |

| W(bit[3]) | 禁止/使能写缓存 0:禁止写缓存 1:使能写缓存 如果 |

- 基于闪烁存储器的TMS320VC5409 DSP并行引导装载方法(05-23)

- DSP外部Flash存储器在线编程的软硬件设计(07-10)

- 一种新型的多DSP红外实时图像处理系统设计(02-03)

- DSP与普通MCU的比较(02-23)

- TMS320C32的存储器接口设计(10-29)

- FM18L08在DSP系统中的应用(01-23)