ARM存储器之:协处理器CP15

| 特 殊 用 途 | ||

| 0 | ID编号(只读) | ID和Cache类型 |

| 1 | 控制位 | 各种控制位 |

| 2 | 存储器保护和控制 | MMU:地址转换表基地址 PU:Cache属性设置 |

| 3 | 内存保护和控制 | MMU:域访问控制 PU:写缓存控制 |

| 4 | 内存保护和控制 | 保留 |

| 5 | 内存保护和控制 | MMU:错误状态 PU:访问权限控制 |

| 6 | 内存保护和控制 | MMU:错误状态 PU:保护区域控制 |

| 7 | Cache和写缓存 | Cache和写缓存控制 |

| 8 | 内存保护和控制 | MMU:TLB控制 PU:保留 |

| 9 | Cache和写缓存 | Cache锁定 |

续表

| 寄存器编号 | 基 本 作 用 | 特 殊 用 途 |

| 10 | 内存保护和控制 | MMU:TLB锁定 PU:保留 |

| 11 | 保留 | 保留 |

| 12 | 保留 | 保留 |

| 13 | 进程ID | 进程ID |

| 14 | 保留 | 保留 |

| 15 | 芯片生产厂商定义 | 芯片生产厂商定义 |

15.1.3 寄存器c0

寄存器c0包含的是ARM本身或芯片生产厂商的一些标识信息。当使用MRC指令读c0寄存器时,根据第二个操作码opcode2的不同,读出的标识符也是不同的。操作码与标识符的对应关系如表15.2所示。寄存器c0是只读寄存器,当用MCR指令对其进行写操作时,指令的执行结果不可预知。

表15.2 操作码和标识符的对应关系

| 操作码opcode2 | 对应的标识符寄存器 |

| 0b000 | 主标识符寄存器 |

| 0b001 | Cache类型寄存器 |

| 其他 | 保留 |

在操作码opcode2的取值中,主标识符(opcode2=0)是强制定义的,其他标识符由芯片的生产厂商定义。如果操作码opcode2指定的值未定义,指令将返回主标识符。其他标识符的值应与主标识符的值不同,可以由软件编程来实现,同时读取主标识符和其他标识符,并将两者的值进行比较。如果两个标识符值相同,说明未定义该标识符;如果两个标识符值不同,说明定义了该标识符,并且得到该标识符的值。

(1)主标识符寄存器

当协处理器指令对CP15进行操作,并且操作码opcode=2时,处理器的主标识符将被读出。从主标识符中,可以确定ARM体系结构的版本型号。同时也可以参考由芯片生产厂商定义的其他标识符,来获得更详细的信息。

在主标识信息中,bit[15:12]区分了不同的处理器版本:

· 如果bit[15:12]为0x0,说明处理器是ARM7之前的处理器;

· 如果bit[15:12]为0x7,说明处理器为ARM7处理器;

· 如果bit[15:12]为其他值,说明处理器为ARM7之后的处理器。

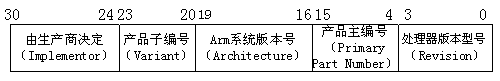

对于ARM7之后的处理器,其标识符的编码格式如图15.2所示。

其中各部分的编码含义说明如下。

bit[3:0]:包含生产厂商定义的处理器版本型号。

bit[15:4]:生产厂商定义的产品主编号,可能的取值为0x0~0x7。

bit[19:16]:ARM体系的版本号,可能的取值如表15.3(其他值由ARM公司保留将来使用)所示。

图15.2 ARM7之后处理器标识符编码

表15.3 bit[19:16]与ARM版本号

| 可能的取值 | 版 本 号 |

| 0x1 | ARM体系版本4 |

| 0x2 | ARM体系版本4T |

| 0x3 | ARM体系版本5 |

| 0x4 | ARM体系版本5T |

| 0x5 | ARM体系版本5TE |

bit[23:20]:生产厂商定义的产品子编号。当产品主编号相同时,使用子编号区分不同的产品子类,如产品中不同的cache的大小。

bit[31:24]:生产厂商的编号现已定义的如表15.4所示。其他的值ARM公司保留将来使用。

表15

- 基于闪烁存储器的TMS320VC5409 DSP并行引导装载方法(05-23)

- DSP外部Flash存储器在线编程的软硬件设计(07-10)

- 一种新型的多DSP红外实时图像处理系统设计(02-03)

- DSP与普通MCU的比较(02-23)

- TMS320C32的存储器接口设计(10-29)

- FM18L08在DSP系统中的应用(01-23)