ARM存储器之:协处理器CP15

.4 bit[31:24]值与ARM生产厂商

| 可能的取值 | ARM芯片生产厂商 |

| 0x41(A) | ARM公司 |

| 0x44(D) | Digital Equipment |

| 0x69(i) | Intel公司 |

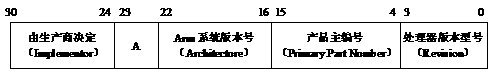

对于ARM7系统的处理器,其主标识符的编码如图15.3所示。

图15.3 ARM7处理器标识符编码

其中各部分的含义说明如下。

bit[3:0]:包含生产厂商定义的处理器版本型号。

bit[15:4]:生产厂商定义的产品主编号,其最高4位的值为0x7。

bit[22:16]:生产商定义的产品子编号。当产品的主编号相同时,使用子编号区分不同的产品子类,如产品中不同的产品子类、不同产品中高速缓存的大小。

bit[23]:ARM7处理器支持下面两种ARM体系的版本号。0x0代表ARM体系版本3;0x1代表ARM体系版本4T。

bit[31:24]:生产厂商的编号已定义的如表15.5所示,其他的值ARM公司保留将来使用。

表15.5 bit[31:24]值与ARM生产厂商

| 可能的取值 | ARM芯片生产厂商 |

| 0x41(A) | ARM公司 |

| 0x44(D) | Digital Equipment |

| 0x69(i) | Intel公司 |

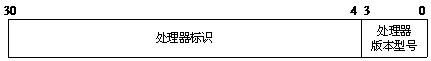

对于ARM7系统的处理器,其主标识符的编码如图15.4所示。

图15.4 ARM7之前处理器标识符编码

其中各部分的含义说明如下。

bit[3:0]:包含生产厂商定义的处理器版本型号。

bit[31:4]:处理器标识符及其含义如表15.6所示。

表15.6 ARM之后处理器标识符与含义

| 处理器标识符 | 含 义 |

| 0x4156030 | ARM3(体系版本2) |

| 0x4156060 | ARM600(ARM体系版本3) |

| 0x4156061 | ARM610(ARM体系版本3) |

| 0x4156062 | ARM620(ARM体系版本3) |

(2)Cache类型标识符寄存器

如前所述,对于指令MRC来说,当协处理器寄存器为r0,而第二操作数opcode2为0b001时,指令读取值为Cache类型,即可以用下面的指令将处理器的Cache类型标识符寄存器的内容读取到寄存器r0中。

MRC P15,0,r0,c0,c0,1

Cache类型标识符定义了关于Cache的信息,具体内容如下所述。

· 系统中的数据Cache和指令Cache是分开的还是统一的。

· Cache的容量、块大小以及相联特性。

· Cache类型是直(write-through)写还是回写(write-back)。

· 对于回写(write-back)类型的Cache如何有效清除Cache内容。

· Cache是否支持内容锁定。

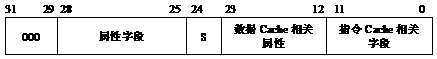

Cache类型标识符寄存器各控制字段的含义编码格式如图15.5所示。

图15.5 Cache属性寄存器标识符编码格式

其中各控制字段的含义说明如下。

属性字段(ctype):指定没有在S位、数据Cache相关属性位、指令Cache相关属性类中指定的属性,其具体编码参见表15.7。

表15.7 Cache类型标识符寄存器属性字段含义

| 编 码 | Cache类型 | Cache内容清除方法 | Cache内容锁定方法 |

| 0b0000 | 直写 | 不需要内容清除 | 不支持 |

| 0b0001 | 回写 | 数据块读取 | 不支持 |

| 0b0010 | 回写 | 由寄存器定义 | 不支持 |

| 0b0110 | 回写 | 由寄存器定义 | 支持格式A,见后 |

| 0b0111 | 回写 | 由寄存器定义 | 支持格式B,见后 |

S位:定义系统中的数据Cache和指令Cache是分开的还是统一的。如果S=0,说明指令Cache和数据Cache是统一的,如果S=1,则说明数据Cache和指令Cache是分离的。

数据Cache相关属性:定义了数据Cache容量、行大小和相联(associativity)特性(如果S≠0)。

指令Cache相关属性:定义了指令Cache容量、行大小和相联(associativity)特性(如果S≠0)。

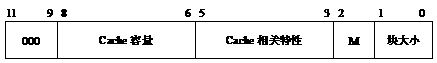

数据Cache相关属性和指令Cache相关属性分别占用控制字段[23:12]和[11:0],它们的结构相同,图15.6以指令Cache为例,显示了编码结构。

图15.6 指令Cache编码结构

其中,各部分的含义说明如下。

bit[11:9]:保留用于将来使用。

bit[8:6]:定义Cache的容量,其编码格

- 基于闪烁存储器的TMS320VC5409 DSP并行引导装载方法(05-23)

- DSP外部Flash存储器在线编程的软硬件设计(07-10)

- 一种新型的多DSP红外实时图像处理系统设计(02-03)

- DSP与普通MCU的比较(02-23)

- TMS320C32的存储器接口设计(10-29)

- FM18L08在DSP系统中的应用(01-23)