高性能定点DSP位处理单元(BMU)设计

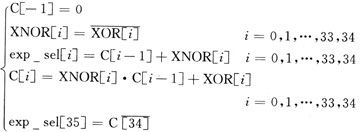

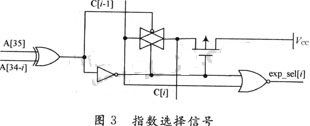

34)的移位选择信号可以表示成XOR[i]和C[i-1]的函数,指数选择信号的最高位exp sel[35]可以表示成C[34]的反信号,这表示如果前35位屏蔽信号都为0,则屏蔽信号C[34]无效,此时exp sel[35]=1;如果前35位已经有一个为1,则说明36位二进制位中存在与BMUi[35]相异的位,此时屏蔽信号C[34]有效,exp-sel[35]被屏蔽。综上所述,得到第i级的指数选择信号exp-sel[i]和提供给下一级的屏蔽信号C[i]如下式所示,设计电路如图3所示。

由图3可以看出,屏蔽信号最多将会经过30几级传输门,是取指电路的关键路径,经过30几级的传输门后,信号驱动能力较弱,延时较大,不符合高性能DSP的要求。可以考虑将这最长路径打断,提高速度。类似与超前进位加法器的进位传递,将屏蔽信号链打断,每4位提供一个超前屏蔽信号,用来屏蔽下一级的移位选择信号,这样隔断了最长路径,提高了驱动能力,进而提高取指电路的工作速度。

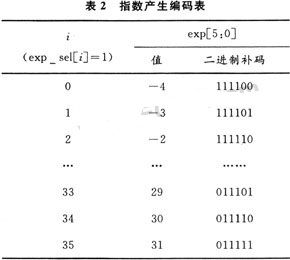

指数选择信号产生后,只要经过相应的编码就可以得到相关的指数值(二进制补码),编码表如表2所示。

2.3 移位选择处理

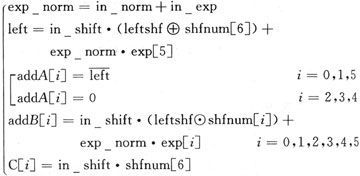

移位选择处理是根据移位数目shfnum和指数exp来产生移位选择信号shfsel。移位选择处理过程主要是根据输入控制信号(in norm,in shift,in leftshf)以及移位数目shfnum和指数exp产生两种信号:最终左移信号left和最终左移数目leftnum。经过分析,left和leftnum都可以写成输入控制信号、指数exp和移位数目shfnum的逻辑表达式。进一步分析表明,可以用6 b(因为最终的移位选择信号是36位,至少需用6位来表示)的加法器来产生leftnum。最终移位信号left以及加法器的被加数addA、加数addB和进位c[i]的逻辑表达式(下式)。将leftnum进行译码后就可以得到移位选择信号shfsel。

2.4 移位数据处理

该处理过程主要是产生桶形移位器的71位输入数据D[70:0],将71位数据位分成两部分,一部分叫原数据位(36位,放置经过处理的输入数据),另一部分叫扩展数据位(35位,放置考虑了逻辑右移等的扩展位)。由桶形移位器的原理可以知道,当最终左移信号有效(即left=1)时,D[70:35]为原数据位,由原36位输入数据填充,低35位D[34:0]为扩展数据位,用0来填充。而当最终左移信号无效(即left=0)时,此时需分两种情况考虑:

(1)如果是算术移位,则D[35:0]为原数据位,由原36位输入数据填充,而D[70:36]是扩展数据位,由符号位扩展形成;

(2)如果是逻辑移位,此时是将原36位数据的低32位右移,高位补0,鉴于此,需要将原36位数据的高4位清零后赋给原数据位D[35:0],高35位(即D[70:36])由0扩展形成。

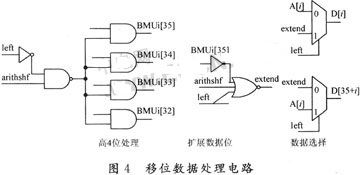

由上述分析,移位数据处理电路可以分成3部分设计:原36位输入数据的高4位处理电路,扩展数据位电路,数据选择电路。分别设计这3部分电路如图4所示。

3 电路模拟

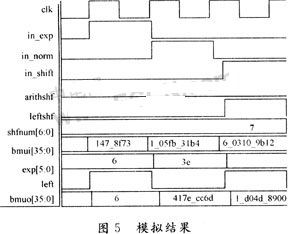

电路模拟工作在Sun Fire V880 Solaris系统环境下完成,模拟采用CSMC.5单阱CMOS工艺模型,环境温度25℃,工作电压为5 V。电路模拟采用VCS+NanoSim混合仿真的方法进行,由VerilogHDL提供激励给BMU的网表。模拟结果如图5所示:当bmui=0x1478f73时,exp=6,bmui=0x105fb31b4时,归一化后bmuo=417ecc6d,当bmui=0x603a09b12,shfnum=7左移时bmuo=ld04d8900。这表明BMU功能符合设计目标,同时测得BMU的最大延时是8.78 ns,即极限工作频率是114 MHz。NanoSim自动生成的状态记录文档指出本文设计的BMU共使用了4 527个晶体管。

4 结 语

本文设计了用于定点DSP的位处理单元电路,他有效地实现了逻辑/算术移位、取指、归一化等操作,解决了利用定点DSP进行浮点运算的问题。该BMU包括桶形移位器、取指电路、移位数据处理电路和移位选择处理电路等几部分。在设汁取指电路时,借鉴超前进位加法器中超前进位的概念.采用了超前屏蔽,将最长路径打断,提高了电路的工作速度。另外,该BMU仅包含4 527个晶体管,资源消耗较少,在5 V工作电压下,电路速度达到114 MHz,完全符合高性能DSP的要求。

- 基于DDS+PLL高性能频率合成器的设计与实现(04-24)

- 基于多内核处理器ADSPBF561的高性能视频控制系统设计(02-16)

- DSP如何实现高性能的处理(上)(01-05)

- 高性能多DSP互连技术研究(01-28)

- 全新6核DSP:低功耗高性能一个都不能少(04-04)

- 基于高性能多DSP互连技术研究(04-02)