一种嵌入式系统实现的JTAG调试器

个指令执行周期, 将寄存器R0的值放到数据总线上去。对ARM寄存器写操作及访问内存的方法与此类似,都是通过扫描链1, 只是所使用的指令不同而已。

网络编程

通过网络编程, 可以对目标系统实现远程调试。图4是PC与仿真器的网络通信流程图。网络通信通过μClinux下的socket编程实现, 首先PC(调试主机)通过网络向仿真器发送命令, 仿真器通过统一的程序接口分析调试命令, 并将调试命令转换成JTAG标准所要求的时序, 通过I/O口线发送到目标板; 然后目标板执行命令,并将命令执行后得到的调试信息返回给仿真器, 接着仿真器将调试信息通过网络发送给PC, 这样用户在PC上便得到了调试信息。

JTAG调试器测试及部分执行结果

本设计最终完成了一种在Linux终端下操作的JTAG调试器。调试器上电后便在μClinux 下自动运行调试器客户端程序, 同时在PC的Cygwin环境下运行JTAG调试器服务器端程序jtager , 建立网络连接。然后在Cygwin下键入用户调试命令, 执行下列操作: (1)写目标板上的CPU状态; (2)读写编址在统一内存空间的外部设备寄存器; (3)读写目标机上的RAM; (4)读写目标机上的固态存储设备, 如Flash; (5)对嵌入式ICE- RT进行调试。

设计实现的调试器的用户命令较多, 下面仅列出两条典型命令IDCODE 和REG 执行后的结果。

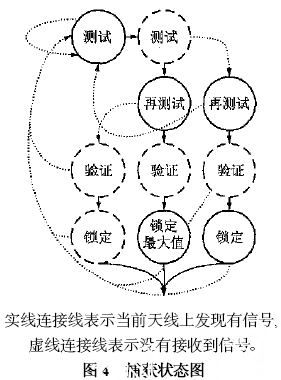

执行IDCODE命令后, 读出了一个基于S3C4510B的目标开发板内的CPUID号, 从而得到Device ID="0x1F0F0F0F"。通过逻辑分析仪分析几个JTAG接口信号的时序关系, 可以观察到JTAG扫描连的访问过程以及该过程中各种状态的转移, 结果与JTAG_调试原理吻合。

执行RE命令后, 得到了寄存器R0~R15及CPSR内容, 即读出了目标开发板处理器S3C4510B在当前处理器模式下的所有寄存器值, 而且还可以通过其他命令对其进行修改。

此外, 通过扫描链2可以访问嵌入式ICE- RT的17个宽度不同的内部调试寄存器, 通过这些寄存器使目标ARM7TDMI分别进入调试状态的3种方式, 即控制DBGRQ信号、断点和观察点, 实现在线调试功能。

本文实现的JTAG调试器具有基本的调试功能, 尚不具备完善的用户操作界面, 特别是图形操作界面, 另外网络功能也需要进一步完善。但调试器的设计和实现方法对于设计类似调试器具有参考价值。为了提高JTAG调试器速率, 还可以采用CPLD或FPGA实现JTAG时序,通过存储器形式与调试器CPU接口, 这将在提高速度的同时, 减轻调试器CPU的负担。

- 基于JTAG的DSP外部FLASH在线编程与引导技术(01-22)

- 采用DSP的声音采集系统硬件原理及设计(04-28)

- AVR单片机介绍(07-09)

- 总线实现片内硬件调试支持单元设计(08-15)

- 多核处理器架构及调试方案(03-28)

- 基于JTAG口对DSP外部Flash存储器的在线编程设计(04-29)