基于TMS320F2812的多轴运动控制卡设计

引 言

开放式体系结构的数控系统已成为当今数控技术的发展方向,而其中的基于计算机标准总线的"PC+运动控制卡"结构则是今后开放式数控技术发展的主流。此类数控系统通常选用高速DSP作为运动控制卡CPU,采用主从式控制策略,利用PC和DSP都读取内存的方式来实现上/下位机的通信;具有信息处理能力强、开放程度高、运动轨迹控制准确、通用性好等特点,被广泛应用于制造业自动化控制各个领域。

1 硬件电路总体设计

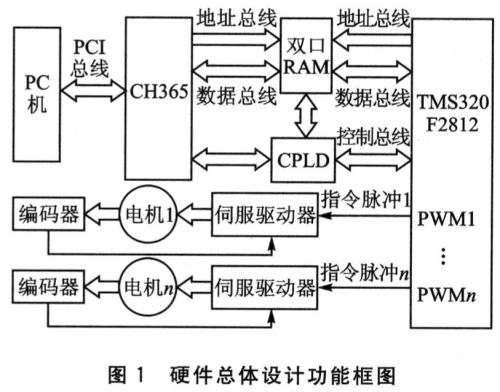

本项目是设计一款基于PCI总线的,以DSP芯片TMS320F2812为核心的多轴运动控制卡。将PC机的信息处理能力和开放式的特点与运动控制器的运动轨迹控制能力有机地结合在一起,利用双口RAM作为公共存储单元实现上/下位机的通信。为实现对多电机的半闭环控制提供了一个良好的开发平台。

系统中,PC机发送各种控制命令,经PC程序进行译码、预处理等处理后,通过PCI总线接口芯片传送到公共存储器--双口RAM中;DSP程序从双口RAM中读取指令或数据,并根据读入的指令或数据进行插补运算,然后产生位置控制脉冲输入到各个电机轴的伺服驱动器;伺服驱动器根据DSP发送的位置指令再进行插补,同时由插补运算计算的理论位置与位置反馈模块反馈的实际位置进行比较,得到跟随误差,经误差补偿后形成真正的电机实际位置,并由跟随误差算出速度指令值,最后产生PWM脉冲控制电机运行。在本系统中,TMS320F2812芯片作为总控制器,统筹协调数控系统中各个轴的运动,而伺服驱动器则作为执行元件控制每个电机的实际运行。运动控制卡与伺服驱动器各司其职,相互配合,都发挥了各自的长处。由此组成的数控系统开放性好,可靠性高,能够很好地满足现阶段大多数用户对多轴联动数控系统的要求。

系统硬件总体设计功能框图如图1所示。

本系统的运动控制卡所选用的DSP芯片TMS320F2812有2个事件管理器(EVA、EVB),每个事件管理器可以产生5路独立的PWM信号,其中比较寄存器3路,通用定时器2路。理论上讲,1片TMS320F2812芯片最多可以控制10个伺服驱动器。而常见的数控系统有三轴联动、五轴联动等,运动控制卡可以控制的电机数目远大于一个数控系统中电机的数目。因此,本系统的"PC+运动控制卡"数控系统不仅能够满足多轴联动数控系统的基本要求,还具有很高的扩展性,甚至可以实现多个数控机床联合控制,极大地增强了多轴联动数控系统的功能。

2 双口RAM接口电路设计

2.1 双口RAM与DSP和CH365的连接

本系统选用双口RAM芯片IDT7025作为DSP与CH365双向通信的缓冲芯片。IDT7025芯片是一款高速的8K×16位双口静态RAM,它提供2个独立的端口,允许两个(左、右)端口同时读/写数据,每个端口具有自己独立的控制信号线、地址线和数据线,可高速存取数据,可与大多数高速处理器配合使用,而无需插入等待状态。

双口RAM允许2个CPU同时读取任何存储单元(包括同时读同一地址单元),但不允许同时写或一读一写同一地址单元。利用双口RAM进行通信的关键是,如何处理好争用冲突现象,避免由此而产生的读/写错误。常用的双口RAM解决地址竞争的途径有:令牌传递法、基于邮箱机制的INT中断法以及插入等待周期的BUSY法等。本系统采用第2种方法。

下面简要介绍一下IDT7025中断的原理:当用户要用到中断功能时,内存中的1FFE和1FFF单元将作为中断标志邮箱传递命令信息。当左端口定义为写状态(CEL=R/WL=VIL),且在内存1FFF中进行写操作时,右端口的中断标志INTR为低电平,可以向右端口发出中断请求;当右端口对地址1FFF进行访问时(CER=OER=VIL),无论读写都可以清除右端口中断标志INTR。相反也是一样的,当右端口对内存1FFE进行写操作时,左端口可以发出中断请求;当左端口访问地址1FFE时,清除左端口中断标志。使用中断时,向1FFF和1FFE写的内容由用户自行定义,本系统中设定:申请中断时向邮箱写入1或其他大于O的整数,清除中断时向邮箱写入O。

系统中双口RAM IDT7025作为DSP与PC机之间的共享数据空间,右端口与CH365相连,映射到CH365的存储空间;左端口与DSP相连,映射到TMS320F2812的区域0。由于IDT7025的供电电压为5 V,因此,在DSP芯片与双口RAM芯片之间加入了一个电压转换芯片SN74LVTHl6245,其硬件连接示意图如图2所示。将图2中的双口RAM划为2个存储空间,即PC通过写高4 KB空间向DSP发送指令,DSP通过写低4KB空间向PC机反馈数据。

2.2 数据总线扩展电路设计

由于系统采用了双口RAM作为DSP和CH365之间数据传输的缓冲芯片,而TMS320F2812的地址总线为19位,IDT7025为13位

TMS320F2812 多轴运动 控制卡 相关文章:

- 基于DSP的无刷直流电机调速系统(06-01)

- TMS320F2812在多段液压机械无极变速器中的应用(11-10)

- 基于TMS320F2812的数字化三相变频电源的研制(01-15)

- 基于DSP的高精度数字频率计的设计(02-03)

- 基于TMS320F2812的分布式温度采集记录仪的设计与实现(11-29)

- 基于TMS320F2812的矢量变频调速系统研究(01-15)