基于DSP通讯全桥开关电源的研究与设计

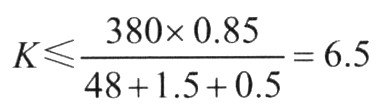

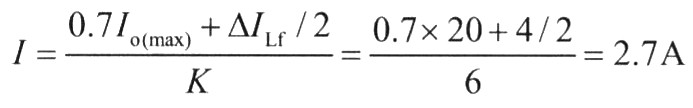

则可根据经验公式

所以实际中取K=7

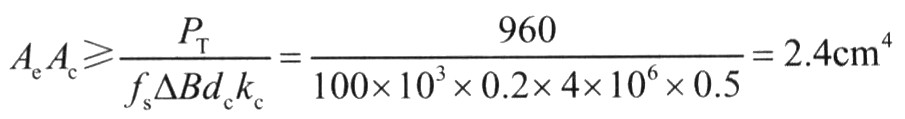

(2)磁芯的计算

在计算好匝比以后,可以根据以下经验公式求解,Ae为磁芯磁路截面积;Ac为磁芯窗口面积;PT为变压器传输功率;fs为开关频率;△B为磁芯材料所允许的最大磁通密度的变化范围;dc为变压器绕组导线的电流密度;kc为绕组在磁芯窗口中的填充因数。并且我们将本设计中电源的参数代入求之得

根据以上的计算并根据铁氧体磁芯生产产家提供的技术手册,我们可以选择PQ50/50磁芯,可以满足要求。

其中Ap=14.2024cm4≥2.4cm4

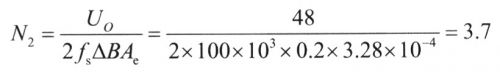

(3)匝数的计算

选取好磁芯后,先计算副边绕组匝数。

选定N2=4,根据匝比我们可以选定N1=28。

(4)导线规格的选择

根据所计算的原副边电流值,并考虑集肤效应,采用电流密度为4A/mm2的导线,可以计算得出所需导线的截面积为0.89mm2的,因此可以采用铜导线来进行绕制,通过分析计算可以得出,我们采用φ0.4铜线8股并绕28圈作为初级绕组,因副边有两组绕组,所以通过它的电流有效值为0.632Io=12.64,所以其绕组截面积为3.16mm2,所以采用φ0.4铜线26股并绕4圈作为次级绕组。

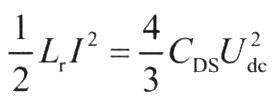

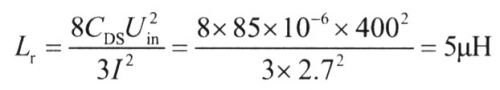

5)谐振电感设计

谐振电感用来实现滞后桥臂的零电压开关,为开关管的零电压开关提供足够的能量。为实现滞后桥臂的零电压开关,必须满足

其中Lr是谐振电感,I是滞后桥臂开关管关断时原边电流的大小,CDS是开关管漏源极电容,Udc是母线直流电压。

其中谐振电感值按0.7倍满载以上实现零电压开关设计,取负载电流为2A(取满载电流的10%)时滤波电感的电流临界连续,即式中的脉动量为4A。开关管IRFB20N50的漏源极电容为85pF。所以将上述结果代入经验公式可以得到

6)输出滤波电路设计

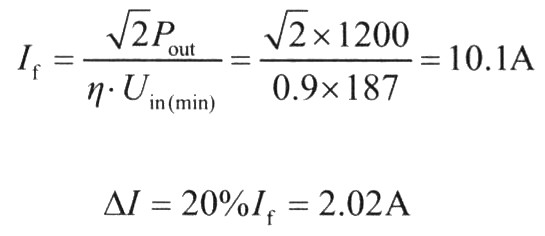

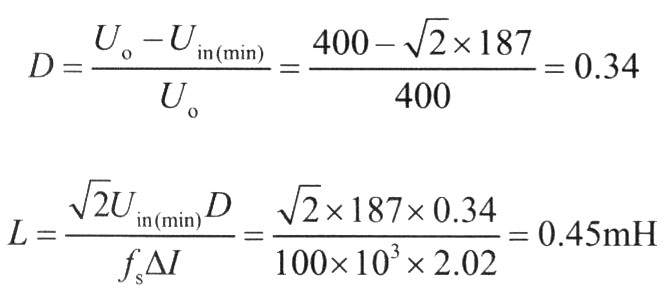

(1)输出电感的选择

电感将决定在输出侧纹波电流的大小,且它的值与纹波电流的大小有关。电感值是以输入侧的交流电流峰值所决定的。而交流侧的峰值电流是出现在电压为最小值时,根据一般的经验考虑电感上的纹波电流取交流侧峰值电流的20%,所以。根据下述经验公式可以得到电感L。

电感电流出现最大峰值时的占空比为

(2)输出电容的选择

输出电容的选择应满足最大输出纹波电压u的要求,而输出纹波几乎完全由滤波电容的等效串联电阻的大小决定,通常通过选择合适的等效串联电阻来满足输出纹波电压的峰一峰值的,这里取u为0.1V。因此有

另外,对于铝电解电容器,在很大容值及额定电压范围内,其ResrCf的乘积基本不变,为50×10-6~80×10-6。根据ResrCf的平均值来求解Cf,即

实际选用三个60V/1000μF的电解电容器并联。

7)采样电路设计

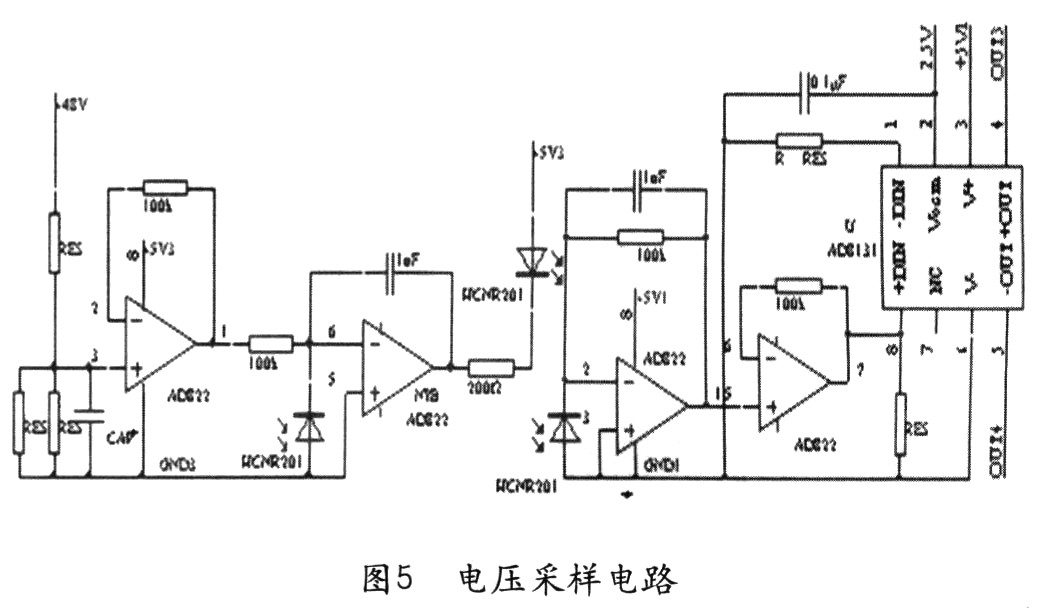

(I)电压采样电路

图5所示的电压采样电路是采样48V输出电压,经过电压跟随电路及线性光耦HCNR20l,传输给差分放大电路AD8131变成差分信号传入高速AD转换器。

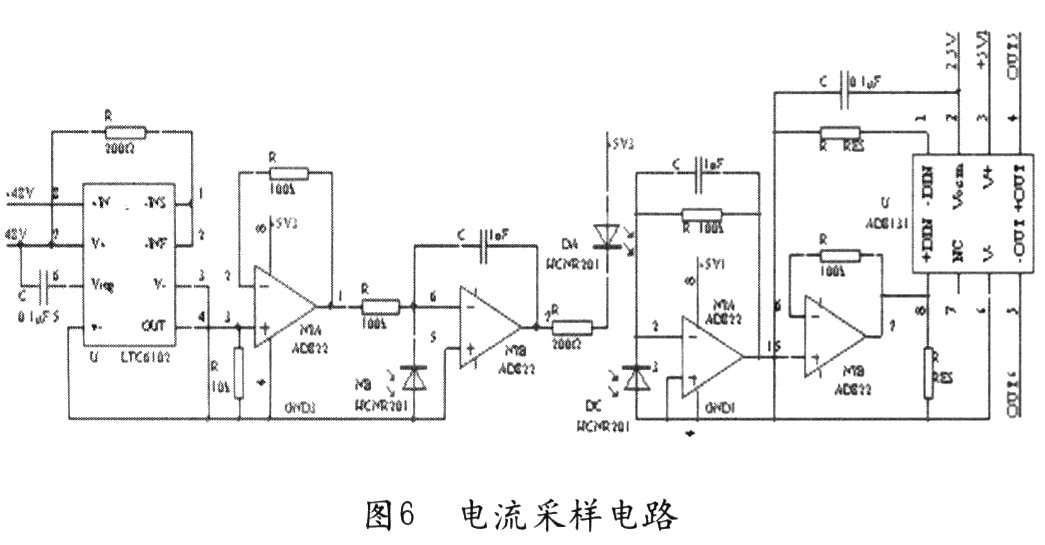

(2)电流采样电路

图6所示的电流采样电路是实时监测输出电流(20A),该采样电路由电流检测放大器LTC6102,基本放大电路,线性光耦HCNR201以及差分放大电路AD813l组成。

3 系统的软件设计

主控制器采用DSP处理芯片,外扩16位高速AD采样,以满足实时要求,控制算法采用模糊自适应PID控制算法。控制程序主要由主程序和中断程序组成。中断包括定时器周期中断、定时器下溢中断、比较单元比较中断。其中,每个比较单元均会在一个对称PWM周期内产生两次匹配,一次匹配在前半周期的递增计数期间,另一次匹配在后半周的递减计数期间,所以两个比较单元会在一个PWM周期内通过四次中断完成PWM输出跳变。

4 模糊自适应PID控制器的设计

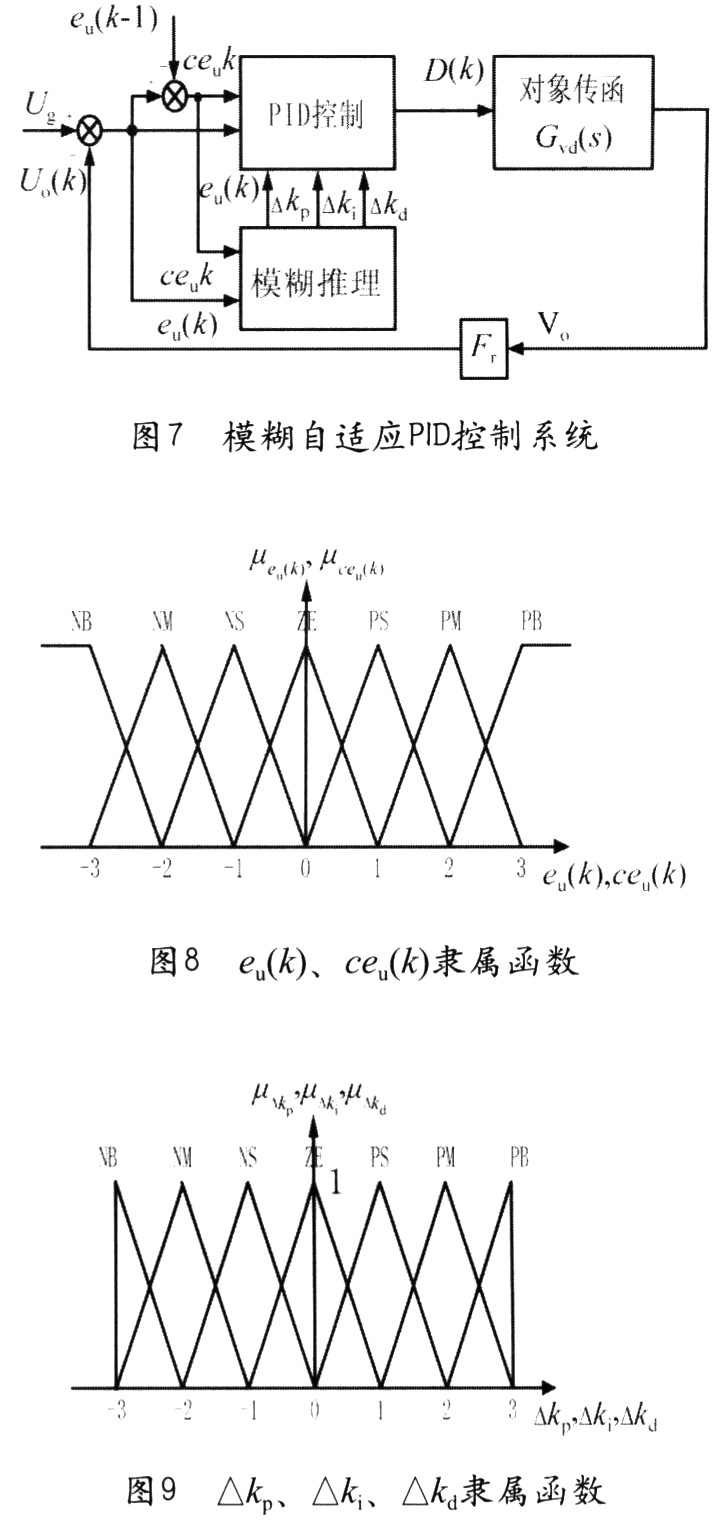

模糊自适应PID控制系统框图如图7所示,该图中模糊自适应PID控制器以电压误差eu(k)和误差变化率ceu(k)作为输入,针对不同情况对PID参数进行调节,模糊推理的输出结果△kp、△ki、△kd与常规PID控制参数kp、ki、kd分别相加,作为修正后的PID参数模糊自适应PID控制的核心在于设计模糊隶属函数和控制规则。首先,确定模糊控制器的输入变量eu(k)和ceu(k)、输出变量△kp、△ki、△kd的模糊集合为7个模糊子集:[正大(PB),正中(PM),正小(PS),零(ZE),负小(NS)、负中(NM),负大(NB)]。各变量的模糊集论域均为[一3,一2,一1,0,1,2,3],实际中通过调节量化因子和比例因子将各变量变化范围映射到论域范围。隶属函数均采用三角形隶属函数,eu(k)、ceu(k),△kp、△ki、△kd的隶属度函数分别表示在图8和图9中。模糊推理采用Mamdani方式,解模糊方法为面积重心法。

5 MATLAB仿真研究

该系统主电路使用MATLAB工具进行相关的仿真,控制算法采用模糊

- 在采用FPGA设计DSP系统中仿真的重要性 (06-21)

- 基于 DSP Builder的FIR滤波器的设计与实现(06-21)

- 达芬奇数字媒体片上系统的架构和Linux启动过程(06-02)

- FPGA的DSP性能揭秘(06-16)

- 用CPLD实现DSP与PLX9054之间的连接(07-23)

- DSP+FPGA结构在雷达模拟系统中的应用(01-02)