基于AD9516的高速四通道时间交叉采样时钟的设计

对于OUT7与OUT9相对于OUT6与OUT8的延时90°,通过调节每个输出通道的AT微小延时模块来实现,相位延时细调是通过对△T模块内的电容充放电获得,延时时间可通过电容量和电流值计算。

3 软件编程

根据AD9516的工作原理,正确配置所有寄存器,需要把数据加载到AD9516内部寄存器。AD9516的加载模式为串口同步加载,兼容于SPI标准协议和SSR协议,串行控制端允许对AD9516所有寄存器的配置进行读/写,支持单字节和多字节及高/低位优先顺序模式,AD9516串行控制可以配置为单一的双I/O引脚(SDIO)或两个单向引脚(SDIO/SDO)模式。默认模式下,AD9516为双端模式加载,加载时钟为SCLK。

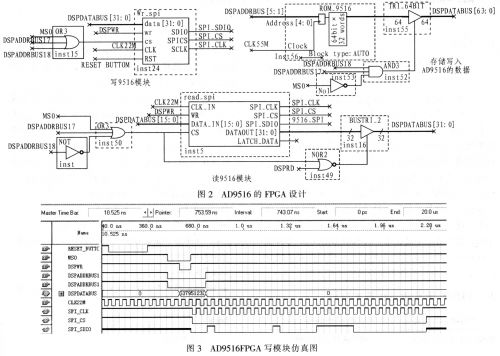

为了便于调试,DSP作为整个读写操作的核心,不管是读数据还是写数据都由DSP完成。写AD9516的软件流程是先把写入寄存器的数值存放在FPGA的ROM中,由DSP通过慢速协议从FPGA读取数据.然后通过DSP写入FPGA的写模块,最后写入AD9516。而读AD9516的软件流程是根据AD9516的读时序,写入读指令,最后由读模块读取AD9516的寄存器数值。具体FPGA设计如图2所示。

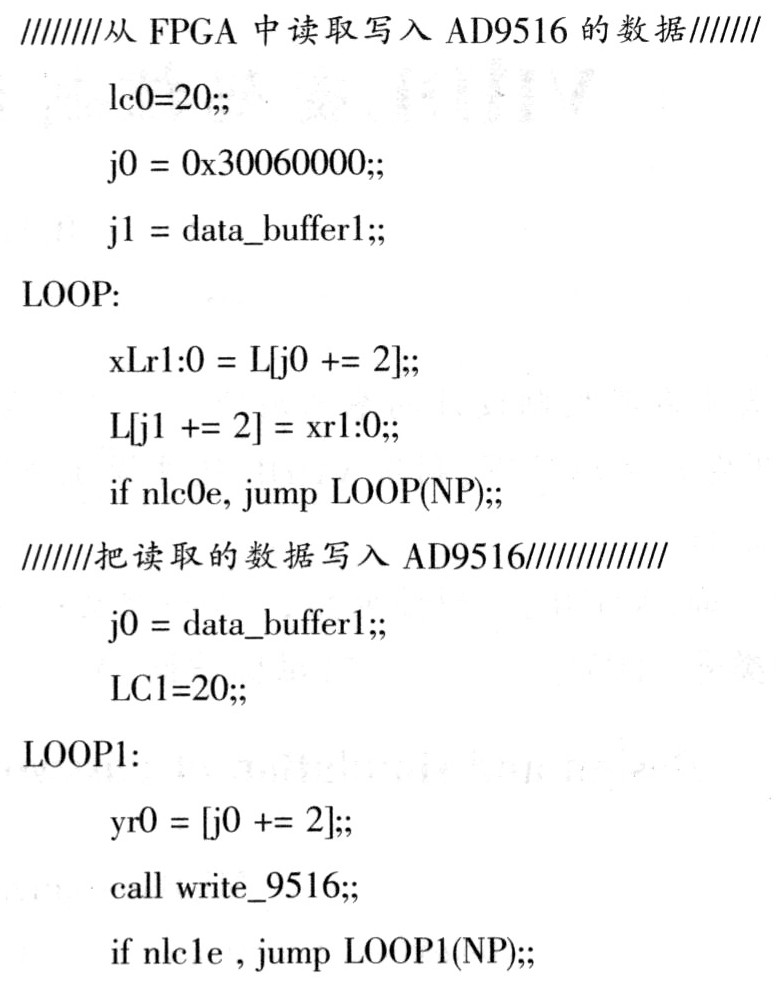

在完成FPGA设计后,由于整个系统控制都是由DSP完成,因此需对DSP进行编程。以下给出部分DSP(TS一201)的写AD9516的程序代码,其中系统寄存器配置为0X189067:64位总线,慢速协议。

最后根据FPGA设计,利用Quartus II仿真,写AD9516模块的软件仿真如图3所示。FPGA采用Ahera公司的STRATIXTM II系列的一款EP2S60F672器件。其仿真结果与AD9516的写时序完全吻合。

4 结语

交叉采样系统时钟源性能是决定整个采样系统指标的关键。基于此,本文提出了利用AD9516给高速A/D转换提供采样时钟的设计方案。实践证明,利用这种方法产生的时钟能够满足四通道A/D转换实现440 MHz的交叉采样的时钟要求,可供其他高速A/D转换的设计人员借鉴。

- 3DES算法的FPGA高速实现(06-21)

- 基于DSP和USB的高速数据采集与处理系统设计(05-01)

- 基于DSP的高速便携红外气体分析仪(05-18)

- 嵌入式编程需注意的Cache机制及其原理(05-25)

- 基于DSP的高速数据采集系统设计方案(06-25)

- DSP在无线传感系统中的应用(01-12)