ADSP-TS201的系统设计及外部总线接口的技术

连接。支持1 024-,512-,256字的页面长度,通过对SDRCON寄存器的编程可实现页面长度的选择。同时SDRAM占用TS201的外部存储空间地址,通过设置/MSSD3~0来确定SDRAM的地址空间范围。

本设计选用的SDRAM是HY57V561620B,页面长度为512字,将两片SDRAM拼接成32位的总线宽度,实现与TS201的无缝接口。根据不同的总线宽度,TS201的地址总线与SDRAM的连接有所不同。

(1)对于32位数据总线其连接方式如下:

SDRAM地址Bit9~0与TS201 ADDR9~0相连;

SD

RAM地址Bitl0与TS201的SDA10管脚相连;

SDRAM地址Bitl5~11与TS201 ADDRl5~11相连。

(2)对于64位数据总线,连接方式如下:

SDRAM地址Bit9~0与TS201 ADDRl0~1相连,TS201 ADDR0悬空;

SDRAM地址Bitl0与TS201的SDAl0管脚相连;

SDRAM地址Bitl4~11与TS201 ADDRl5~12相连。

另外对于标准的SDRAM(3.3 V),TS201的地址线ADDRl5∽11都可以作为BANK的选择线。对于低功率的SDRAM(2.5 V),只有ADDRl5~14可以作为BANK的选择线。因此在进行接VI设计时一定要注意所选择SDRAM的电参数。

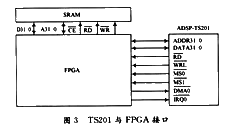

4.2 ADSP-T$201与FPGA接口

本文设计的系统需要将FPGA连接在TS201的外部总线上,采用DMA中断,通过总线的方式从FPGA的外挂RAM(乒乓存储)中读取数字下变频后的I,Q两路数据,其连接方式如图3所示。

其中MS0,MS1是片选信号,RD和WRL分别是读和写信号。在一个PRF周期内FPGA进行数字下变频,将I,Q数据存储到SRAM中,然后向 TS201发出DMA请求,TS201将SRAM的数据采用流水线协议通过总线读入片内RAM中,进行后续的处理。再将处理完的数据以总线方式写入到FPGA内部RAM中,以便进行在线仿真或者进行后续的输出。

5结 语

本文主要结合ADI公司的高性能ADSP-TS201的结构特点,讨论了在系统设计的过程中应该重点注意的几个问题和ADSP-TS201的外部接口技术,并给出了其与SDRAM,FPGA的连接实例,对基于TigerSHARC系列DSP的应用设计具有实用的参考价值。

ADSP-TS201 系统设计 外部总线接口 相关文章:

- 基于ADSP-TS201S的多DSP并行系统(03-06)

- 基于ADSP-TS201S的二维DMA数据传输(03-08)

- 基于CPCI总线的多片ADSP-TS201引导设计(09-20)

- 图形化系统设计:缩短开发时间的嵌入式设计(11-22)

- 基于ARM与DSP的智能仪器系统设计(01-05)

- 基于SBC与DSP的嵌入式系统设计(01-22)