基于CPCI总线的多片ADSP-TS201引导设计

摘要:分析了ADI公司TigerSHARC系列数字信号处理器ADSP-TS201的引导方式,设计实现了基于该DSP处理器的某雷达信号处理机的自动引导方案。与其他加载方式相比,该引导方案采用CPCI总线向板卡传输引导代码,进而通过链路口引导DSP自启动,具有程序加载方便,调试修改灵活的特点。

关键词:ADSP-TS201;引导程序;CPCI总线;链路口

0 引言

数字信号处理器DSP是一种具有特殊结构的微处理器,它专门为实现数字信号处理的各种算法而设计,因而在硬件结构上具有特殊性。TS201是ADI公司TigerSHARC系列中集成了定点和浮点计算功能的高速DSP。该处理器广泛应用于视频、通信市场和国防军事装备中,适合于大数据量实时处理的应用领域。

TigerSHARC系列DSP引导程序的加载方法非常灵活,可根据实际系统的需求灵活选用。某雷达信号处理机采用6U板形,CPCI总线采用欧洲卡尺寸标准,通过CPCI总线与主机进行数据通信。针对该信号处理机硬件系统,本文提出一种引导方案,该方案采用CPCI总线向板卡传输引导代码,进而依靠FPGA通过链路口引导DSP自启动。

1 ADSP-TS201引导模式

DSP的引导就是在DSP系统复位的情况下从DSP外部存储器装载算法程序代码的过程。TS201支持两种引导模式:主引导(Master Boot)模式和从引导(S|ave Boot)模式。

在主引导模式下,TS201作为主动方,用外部口输出地址,读引导方式选择(引脚为低电平,则选择主引导模式,DSP从外部EPROM或FLASH中加载程序;若 引脚为高电平,则进入从引导模式,DSP为空闲状态,等待主机或链路口加载程序。两种引导模式都有相同的加载过程,具体步骤如下:

引脚为高电平,则进入从引导模式,DSP为空闲状态,等待主机或链路口加载程序。两种引导模式都有相同的加载过程,具体步骤如下:

(1)TS201自动启动一个DMA,自动把256个字(32位)传送到内部存储器的地址0x00~0xFF。

(2)TS201执行上述256个字的指令(加载核),加载核启动其他DMA,把后续指令和数据加载到内部和/或外部存储器中。

(3)加载核自我覆盖,执行DSP算法程序。

本系统引导方案采用从引导模式,通过CPCI总线将代码从主机传至FPGA中,再利用FPGA经过链路口启动DSP。

2 某雷达信号处理机的引导设计方案

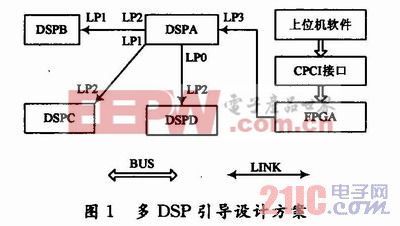

基于某雷达信号处理机硬件处理平台,采用如图1所示的多DSP引导设计方案。

4片DSP的算法程序代码(.LDR文件)通过上位机软件传输到FPGA中,FPGA通过与DSPA的链路口给DSPA加载程序。DSPA加载成功后,分别引导DSPB,DSPC,DSPD启动。

采用这种方式加载DSP的优点:调试DSP时可以不使用JTAG仿真器;同时当DSP自启动时,可以不采用FLASH或E2PROM存放程序代码,对于DSP程序的大小没有限制,也节约了电路板的空间及其硬件设计复杂度。

采用这种方式加载DSP的难点:CPCI总线与FPGA数据传输无误及FPGA与TS201链路口通信,这两个难点在实际工程中都已经解决。CPCI总线与FPGA接口可以采用PLX9656芯片完成数据传输,所以这种加载模式的设计是可行的。

2.1 自动引导程序设计思路

为了设计加载(自动引导)程序,首先必须了解ADSP-TS201的软件设计流程,其流程图如图2所示。

其中,链接描述文件(.LDF)定义了整个系统的存储器配置和程序中数据及代码的具体存放位置。加载核文件(.DEX)是指加载引导核程序,其功能是将用户工程所编译成功的可执行文件(.DXE)合成一个链路口加载方式的输出文件(.LDR)。该加载输出文件用来定义加载过程中TS201的内部和外部存储器如何被初始化。

在VisualDSP++安装目录的ldr子目录下,ADI公司提供了标准加载核文件和相应的源程序(.ASM)和链接描述文件。一般可直接使用提供的标准加载核文件或对其相应的源程序进行简单修改,重新编译链接生成的加载核文件。加载文件是由引导加载器(elfloader)将可执行文件进行一定的格式变化,并在起始位置附加上加载核文件生成的。

由于TS201有三种引导方式(不考虑非引导模式),ADI公司相应地提供了三种不同的加载和文件,分另0为:TS201_prom.dxe,TS201_li-nk.dxe,TS201_host.dxe。三个程序的核心思想和功能完全一致,只是由于使用的加载端口和方式不同,在具体代码实现上稍有差异。由于本系统采用链路口启动,同时对于DSPA,DSPB,DSPC,DSPD都采用不同的链路口启动,因此采用链路口加载核文件,需要对加载核文件稍作修改,满足不用链路口启动的需求。

2.2 本信号处理机的复位引导设计流程

如图1所示,4片DSP要运行的程序最终通过上位机读取后,通过CPCI总线传至FPGA,4片DSP为链路口引导模式。DSP复位后,DSPA从FPGA加载程序,DSPA加载完成后,再分别通过链路口加载DSPB,DSPC,DSPD。加载完成后,4片DSP正常执行各自的程序。

结合以上各部分的分析,可以看出要实现该信号处理机中4片DSP的正确引导,所需的工作由以下几步组成:

(1)由DSPB要执行的程序(DSPB.dxe),结合链路口的加载核程序生成DSPB的加载文件(DSPB_bin.ldr)。需要注意的是,该链路口加载核程序不能直接使用提供的标准链路口加载程序,必须将提供的链路口加载核文件(TS201_link.asm)中的LINK常数改为1(#define LINK 1),即DSPB由链路口1引导。

(2)与(1)类似,生成DSPC的加载文件(DSPC_bin.ldr),只是需要把链路口加载核文件(TS201_link.asm)中的LINK常数改为2(#define LINK 2),即DSPC由链路口2引导。同样DSPD由链路口2加载,同样生成DSPD的加载文件(DSPD_bin.ldr)。

(3)由于DSPA要通过链路口来对DSPB,DSPC,DSPD进行程序引导,所以在进行DSPA编程时,需要在程序的最开始添加给后面所有ADSPTS2 01的引导程序。而每片ADSP-TS201的程序都由引导码和用户程序构成,所以在DSPA给其余DSP传输程序时将传输完整.1dr文件的数据。

DSPA程序流程图如图3所示。

引导 设计 ADSP-TS201 总线 CPCI 基于 相关文章:

- 基于JTAG的DSP外部FLASH在线编程与引导技术(01-22)

- DSP芯片TMS320C6712的外部内存自引导功能的实现(08-30)

- WinCE启动失败原因与解决办法(03-01)

- MCU+DSP嵌入式平台的i机接口与引导设计 (06-25)

- ARM系统预引导固件的新机遇- UEFI(07-12)

- BLOB启动流程分析及引导程序可移植性研究(07-25)