星载交换机高性能队列管理器的设计与实现

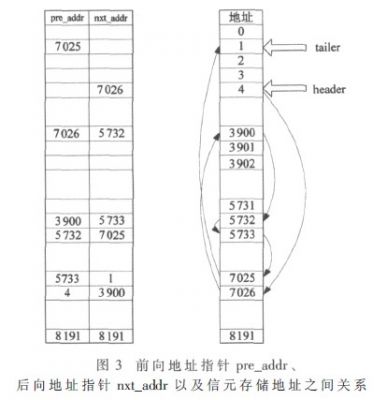

在本队列管理器设计中,交换机的端口数目和信元的优先级可以根据星载交换机的设计要求和交换容量进行动态地扩展,私有区和共享区的存储容量也可以根据流量管理的要求进行动态地扩展。前向地址指针pre_addr、后向地址指针nxt_addr利用FPGA内置RAM实现;PFIFO1、PFIFO2,…,PFIFOK和SFIFO利用FPGA内置FIFO实现;队首寄存器header和队尾寄存器tailer利用寄存器实现。

3 队列管理器工作方法

当系统复位后,队列管理器对地址空间进行初始化,将可用的地址指针写入到地址空间。信元存储空间分为两部分,一部分为共享存储空间,另一部分为K个针对每个端口固定分配的信元空间,以确保每个端口都有可用的存储空间。当一个信元到达时,如果固定分配的空间和共享空间剩余容量之和不能满足该信元时,则拒绝该信元。队列管理器只需要知道到达信元的输出端口和优先级,就可以确定其进入哪个逻辑队列。信元的写入和读出采用状态机进行控制。

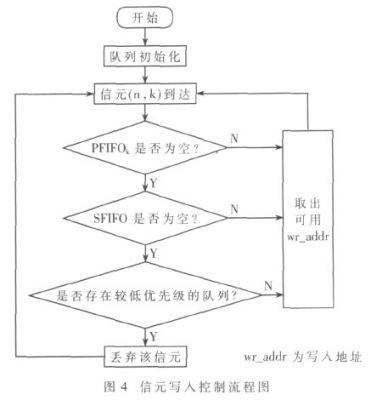

当有新的信元(n,k)到达时,其中n为优先级,1≤n≤N;k为输出端口,1≤k≤K。信元写入控制流程如图4所示。最后根据wr_addr,将信元写入缓冲区。如果发生队列挤占,则被挤占的逻辑队列需要被更新,如果仅有一个信元,则header和tailer都被置0;反之,用前一个信元的地址来更新tailer。写入信元的逻辑队列需要被更新:如果该逻辑队列没有信元,则header和tailer都被置为wr_addr;反之,将tailer的内容记录在pre_addr的第wr_addr个地址中,将wr_addr记录在nxt_addr的第tailer个地址中,tailer的内容被更新为wr_addr。

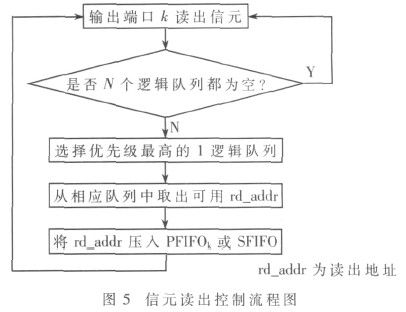

当有信元读出时,各输出端口采用轮询的方式,信元读出控制流程如图5所示。读出信元的逻辑队列需要被更新:如果仅有一个信元,则header和tailer都被置0;反之,用下一个信元的地址来更新header,tailer不变。

4 仿真结果

本设计采用Xilinx Vertex-5 FPGA实现,开发环境是Xilinx集成开发环境ISE13.1,电路核心模块用Verilog HDL编程实现,仿真工具采用ModelSim SE。星载交换机有16个输出端口,信元有4个优先级,PFIFOk为256,SFIFO为4 096。仿真验证结果表明电路功能符合设计要求。

4.1 寄存器读写指针时序仿真

由仿真时序图6可以看出,初始状态时,PFIFO0、PFIFO2、…、PFIFO15和SFIFO都为空,队列管理器将空闲指针依次写入PFIFO0、PFIFO2、…、PFIFO15中,当它们都为满时,最后写入SFIFO中。

由仿真时序图7可以看出,队列管理器首先从PFIFO0中读出可用指针,当其为空时,就从SFIFO中读出,然后依次从PFIFO0、PFIFO2、…、PFIFO15中读出可用指针。当它们都为空时,则从SFIFO中读出,直到no_ptr=1,说明地址空间无可用指针。

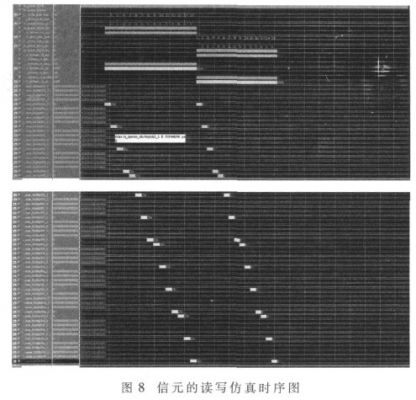

4.2 信元的读写时序仿真

由仿真时序图8可以看出,队列管理器根据信头中的输出端口和优先级,依次将信元写入信元存储器,信元存储器形成64个逻辑队列,然后在调度器的控制下,依次将信元从相应的逻辑队列中读出。

在卫星通信中,业务种类繁多且突发性强,用户对服务质量(QoS)要求较高,而卫星网络拓扑结构变化快,传播时延大,这就要求星载交换机具有较小的交换时延和丢包率。本文设计了一种高性能队列管理器,通过硬件仿真验证,其基本能够满足星载交换机的各种性能指标要求,本队列管理器采用动态扩展的设计方式,灵活度较大,但也存在许多不足之处,如组播信元的处理考虑不足、可能存在队头阻塞问题及IP包的管理问题,有可能由于一个信元的丢失导致整个IP包无法接受,这些都是今后进一步的研究工作。

- uClinux进程调度器的实现分析(04-13)

- 时间触发 合作式调度器 编程模式(10-11)