星载交换机高性能队列管理器的设计与实现

星载交换机是以卫星为核心的天基信息系统的关键子系统,是制约天基信息系统发展的关键技术之一,而星载交换机的核心是高性能的交换芯片。由于太空剧烈变化的环境温度和各种离子的影响,使得宇航级电子器件的性能指标远高于地面设备电子器件,而可选用作为宇航级电子器件的范围又远低于地面设备器件的选用范围,同时星载设备对可靠性的要求远高于地面设备。这就要求星载交换机在技术体制、电路结构、数据包队列管理方式、调度算法等都与地面的交换机有很大不同,这些问题均有待于进行深入研究。

对于以卫星为核心的天基信息系统,利用地面高性能IP交换机仍然存在较大问题,使其在天基信息系统中的使用受到了限制。

(1)功耗:星上设备对功耗有严格的控制,地面高性能骨干IP交换机的功耗通常在数百瓦到几千瓦,这对于星载设备来说是难以承受的。

(2)系统可靠性:星上设备对系统可靠性要求极高,需要在不同层面上考虑冗余备份问题。

(3)系统重量与体积:星上载荷的重量是卫星系统的重要指标,星载高性能交换机在体积和重量上与地面设备相比必须大幅度减轻。

(4)系统硬件结构优化:IP交换机系统的硬件复杂度和集成度非常高,但由于空间温度环境、空间粒子流等的影响,元器件选择上存在很大制约,地面设备中广泛使用的SDRAM、DDR、高性能CPU等器件都无法直接使用,这要求系统硬件结构和算法的复杂度必须降低,使之在可用宇航级元器件(如低速SRAM、处理器和存储器)的基础上实现较高的交换能力。

(5)系统软件结构优化:IP路由器系统的软件复杂度非常高,由于在天基信息系统中高性能网络处理器无法直接使用,所以部分传统上采用软件实现的功能和算法要采用硬件固化的方法来实现。这就需要简化复杂的IP协议栈。

基于以上分析,地面高性能IP交换机在天基信息系统中的使用受到了很大限制。由于星上存储器容量不能像地面那样宽裕,队列长度受限,而卫星空中接口的往返传播时延又大于地面,为了更好地设计流量控制,需要在星载交换机结构中使用一个复杂度低且有效的队列管理器,减少对缓存区容量的要求,保证低时延,降低掉包率,达到用户的QoS要求,提高吞吐量。

1 基本概念

在星载交换机中,为了实现IP数据包快速转发,一般采用基于定长信元的体制,IP数据包在进入交换结构前,被分割成许多固定长度的分组(下文统称为信元)。交换结构的缓存方式主要有输入缓存、输出缓存和共享缓存。对于一个N×N交换结构,输出缓存中存储器的访问速度是线路速率的(N+1)倍;采用共享缓存方式是线路速率的2×N倍;而对于输入缓存方式,存储器的访问速度是线路速率的两倍,与交换机的端口数目无关。为了增大交换机的容量,支持更高的线路速率,在星载交换机中有必要研究输入缓存的方式。

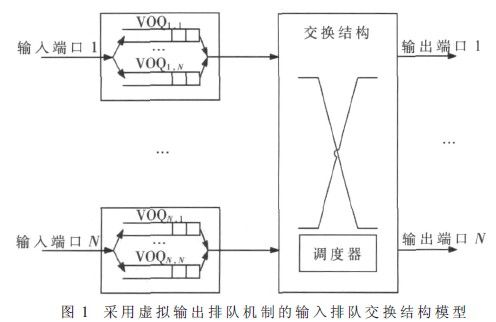

对于输入缓存中存在的队头阻塞HOL(Head of Line blocking)问题,采用虚拟输出排队(VOQ)技术可改善该问题,使吞吐量达到100%。VOQ要获得高的性能,关键问题是要设计一个匹配输入和空闲输出端口的高效、公平的调度算法,也就是二部图的匹配问题。

采用虚拟输出排队机制的输入排队交换结构模型如图1所示。在每个输入端口的缓存区中,设置N个(N为交换机端口数目)FIFO队列,每个FIFO队列对应一个输出端口。也就是说,将输入端口为i,输出端口为j的分组缓存到虚拟输出队列VOQi,j中,在调度器的控制下,将匹配的VOQi,j中的分组调度出去。

2 队列管理器结构

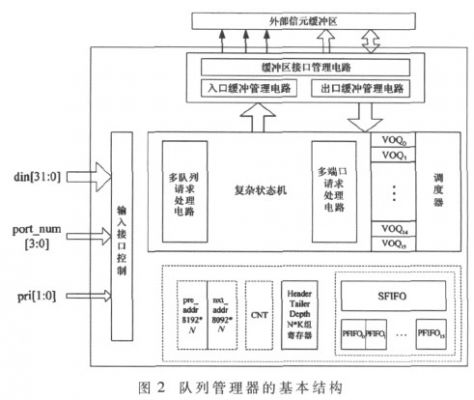

队列管理器由输入控制接口电路、多队列请求处理电路、多端口请求处理电路、缓冲区接口控制电路、调度器等模块组成。队列管理器的基本结构如图2所示。

输入控制接口电路将接收到的IP数据包切割成许多长度为64 B的信元,并做必要的标识,以便进行IP数据包的重组。每个信元都包含一个信头,信头结构包括目的输出端口、优先级和可以扩展的标识。多队列请求处理电路根据信元的输出端口和优先级将信元流分成多个VOQ队列,多端口请求处理电路在调度器的控制下将信元从信元缓冲区读出。

设星载交换机有K个输出端口,信元有N个优先级。信元缓冲区(SRAM)的地址空间被划分成K个私有区和1个共享区。私有区k(1≤k≤K)只能被去往第k个输出端口的信元占用,而共享区可以被去往任何输出端口的信元占用。设置K个私有FIFO(PFIFO1,PFIFO2,…,PFIFOK)和1个共享FIFO(SFIFO)。私有区k(1≤k≤K)的全部可用地址被记录在(PFIFOK)中,共享区的全部可用地址被记录在SFIFO中。

每个输出端口均维持N个逻辑队列,第n(1≤n≤N)个逻辑队列对应于第n种优先级信元。每个逻辑队列由两部分组成;第一部分位于私有区,第二部分位于共享区。逻辑队列可能只存在第一部分,而不存在第二部分。在信元缓冲区中一共形成N×K个逻辑队列。

在电路模块中,设置N×K组寄存器,每个逻辑队列分别使用一组寄存器来控制信元的写入与读出,每组寄存器包括:header、tailer、depth 3个寄存器。其中header为队首寄存器,记录每条逻辑队列的队首地址;tailer为队尾寄存器,记录每条逻辑队列的队尾地址;depth为深度寄存器,记录每条逻辑队列的信元个数。每条逻辑队列中上(前)一个信元和下(后)一个信元的存储地址分别由前向地址指针pre_addr、后向地址指针nxt_addr记录。

图3中给出了前向地址指针pre_addr、后向地址指针nxt_addr以及信元存储地址之间关系的一个示例。图中所示的逻辑队列的队首地址由header记录,队尾地址由tailer记录。该逻辑队列中信元的存储地址依次是4(队首),7 026,3 900,5 732,5 733,7 025,1(队尾)。

- uClinux进程调度器的实现分析(04-13)

- 时间触发 合作式调度器 编程模式(10-11)