TI DSP入门芯片TMS320F28335

完成。EEPROM中的HOLD管脚用来暂停与主设备间串行数据传输,WP管脚则用来进行对EEPROM的写保护,如果其为低电平,则主机无法向其写人数据。系统对两管脚输入高电平,保证EEPROM在读写操作过程中一直可以进行而不被中断。

1.3.3 SCI上位机通信接口

为了实现上位机同DSC异步的通信和数据传输,本系统利用TMS320F28335所提供的SCI接口来完成所需要求。SCI是一个2线的异步串行端口,即常说的UART。其数据的收发支持全双工通信,内部收发均有一个16级的FIFO来缓存数据。为了保证数据可靠,SCI提供奇偶校验,数据溢出检测等操作。SCI接口输出信号的电平是LV-TTL电气标准,通过RS232收发转换器加以驱动,获得RS232电气标准的信号,以便上位机接收。

1.4 模拟电路设计

模拟部分电路主要是以ADC为中心的应用电路。其主要实现模拟信号的处理,采集等工作。其中核心部分为AD转换。

AD转换部分,主要是通过数字采样来完成模拟信号到数字信号的转变。本系统选用的ADC芯片是美国模拟电气公司的AD7656。模数转换芯片AD7656是高集成度、6通道6 bit逐次逼近(SAR)型ADC,内含1个2.5 V基准电压和基准缓冲器。该器件的功耗比最接近的同类双极性ADC降低了60%。AD7656在每通道250kb·s-1采样速率下的精度是同类产品的两倍。可以由引脚和软件选择模拟电压范围:10 V或5 V;模拟电源电压范围为4.75~5.25 V,因而大范围的工作电压使其无需电平转换等其他措施便可以直接与DSC相连;提供有并行和串行接口。可以工作在-40~85℃。标准模式5 V供电,250 kb·s-1时的功耗为140 mW,待机时仅为100μW。基于iCOMS技术制造的AD7656可以满足工业领域对分辨率、多通道、转换速率和功耗等方面的较高要求。

AD7656支持和DSC的并口、串口数据传输,通过SER/PAR SEL管脚的高低电平的选择,来控制采样后数字信号的传输方式。当其为高电平,则使用串行传输方式,反之则使用并行传输方式。本系统选用并行传输方式。在具体的转换过程中,每片AD7656内部的6条采样通路可以分为A、B、C共3组,其中每组通路包含2路通路。3组通路可以同时采样,也可以单独采样,而每组内的两条通路同时采样。管脚CONVSTA,CONVSTB,CONVSTC分别用来对A、B、C采样通路进行控制。当一个上升沿电平到达任一管脚,则该管脚对应模数转换的2路通路被启动,开始完成模数转换。当把三管脚连接,3组采样通路,即所有的6条采样通路同时采样。系统选用3组通路同时采样。

当DSC连接有多片ADC时,则需要通过CS片选管脚来进行ADC的选择。当采样开始,BUSY管脚将从低电平变为高电平,在整个采样的过程中,BUSY一直保持高电平,当采样结束,BUSY则从高电平变为低电平,此时DSC就可以开始读取数据。本系统则利用该管脚作为DSC外部中断源的输入管脚。当BUSY上电平由高变低,则通知DSC产生中断,来进行数据的读取。

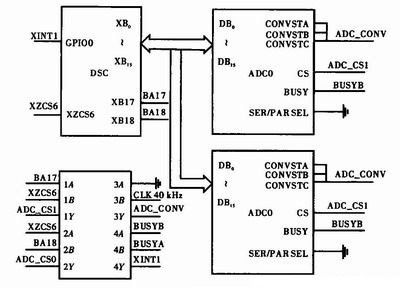

本系统选用2片AD7656完成12路数据采样,通过DSC的XINTF ZONE6把ADC设备映射到DSC上,进行数据传输。通过地址译码和逻辑控制实现2片ADC同DSC的连接。具体结构如图4所示。

图4 系统DSC通ADC连

图4中左下角为逻辑部分,通过DSC的地址线BA17和BA18完成对ADC的选择。可以得到ADC0和ADC1在DSC中的地址映射为0x180000和0x1400 00。而外部输入40 kHz的时钟,作为ADC的采样频率。两个ADC对应DSC的同一个中断,当任意一片ADC采样完毕,都会引起DSC的中断,从而进行采样数据的读取。

2.系统软件设计

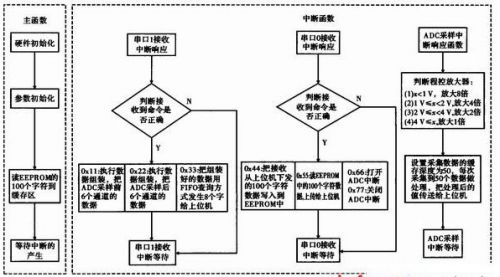

如前所述,整个信号处理板一共有12路模拟信号通路,通过传感器接收到12路模拟信号。2片AD7656把12路模拟信号转换为数字信号传送给TMS320F28335,在TMS320F28335中对这些采集到的数据做相应处理后通过SCI传送给上位机。同时对有必要保存的数据通过SPI接口保存到EEPROM中。整个采集、通信过程由上位机发送相关的命令来加以控制。程序的流程如图5所示。

图5 系统软件流程图

在主函数中,程序首先完成相应模块的初始化,设定好CPU运行的时钟,选定好各个模块的工作模式,然后读取EEPROM中的设备初始化数据,后进行入等待状态。此时CPU等待ADC采样的数据,当ADC采样过程结束,则进入ADC中断响应函数,在此函数中,主要完成数据的读取,对于小信号,通过程控放大器放大其幅值,然后存储到自定义的缓存区中。两个串口工作方式均由上位机发送命令,从而触发SCI的串口收中断服务函数。然后在中断服务函数中完成对应命令要求。系统选用串口1完成采集数据向上位机的传输,串口0完成向EEPROM发送需保存的数据和一些相关操作。而SCI0和SCI1分别对应DSC外设中断

- 在采用FPGA设计DSP系统中仿真的重要性 (06-21)

- 基于 DSP Builder的FIR滤波器的设计与实现(06-21)

- 达芬奇数字媒体片上系统的架构和Linux启动过程(06-02)

- FPGA的DSP性能揭秘(06-16)

- 用CPLD实现DSP与PLX9054之间的连接(07-23)

- DSP+FPGA结构在雷达模拟系统中的应用(01-02)