基于DSP和采样ADC的数字锁定放大器

锁定放大器(LIA)在微弱信号检测领域有着重要的应用,本质上它是一种实现互相关检测的仪器,模拟LIA一般用开关式乘法器和低通滤波器来实现模拟相敏检波,数字LIA是通过ADC将模拟信号转化为数字信号再由DSP或微处理器来进行数字解调运算。数字LIA比模拟LIA有许多优点,如谐波抑制能力强、无直流漂移、实行数字处理有很好的灵活性等。陈佳圭对早期实现数字LIA的5种主要方法进行了介绍,它们的一个共同特点是算法简单、易行,基本上只需做累加运算就可得出检测结果,但它们不能很好地抑制谐波。左营喜等提出的分段累加相关法有一定的灵活性,可在抑制谐波和提高处理速度之间进行折衷。SR850是国外近几年推出的第一代数字LIA产品,其工作原理是通过ADC以256 kHz的固定采样率把被测模拟信号转换为信号序列,由DSP合成正弦参考序列,在DSP中将参考序列和采样得到的信号序列相乘,再进行数字低通滤波得到解调输出。

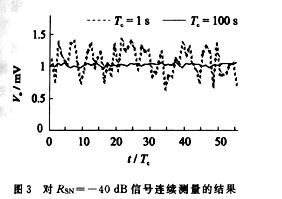

本文给出了一种利用DSP和采样ADC实现数字锁定放大器的方法,与SR850类似,通过采样ADC将被测模拟信号转换为信号序列,由DSP合成参考序列,但不同的是,这里要控制采样频率以实现整周期采样,这样不仅使得DSP可以精确地合成参考序列,而且能建立简洁、有效的数字互相关运算。文中对这种方法进行了分析,并给出了实际设计的数字LIA。

1 工作原理

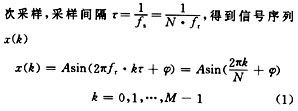

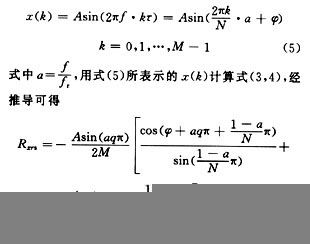

在互相关检测中有一个参考信号,设参考信号频率为fr,可以通过一定方法控制采样频率fs,使得fs=N·fr,N≥3,N由DSP来确定。设被测信号x(t)=Asin(2πfrt+φ),A>0为信号幅度,φ为信号初相位,在q个参考信号周期对x(t)进行M=q·N

不用对实际的参考信号进行采样,而由DSP根据N来合成正弦参考序列rs(k)和余弦参考序列rc(k)

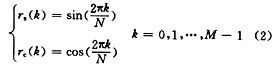

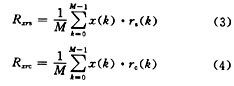

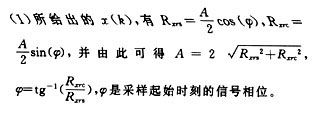

rs(k)和rc(k)分别相当于对正弦参考信号sin(2πfrt)和余弦参考信号cos(2πfrt)进行同步采样所得。按式(3,4)来计算x(k)和rs(k)的互相关Rxrs,x(k)和rc(k)的互相关Rxrc

式(3,4)分别表示同相输出和正交输出,对于由式

2 频率特性

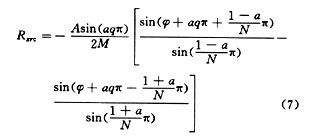

分析输入信号与参考信号不同频时的输出特性。设被测信号x(t)=Asin(2πft+φ),f≠fr,A>0为信号幅度,仍在q个参考信号周期进行M次采样,得到信号序列x(k)

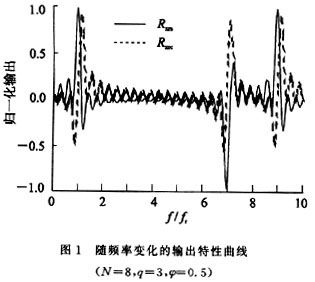

式(6,7)描述了测量非同频正弦信号时的同相输出和正交输出。图1给出了在N=8,q=3,φ=0.5时,根据式(6,7)得到的随频率变化的输出特性曲线。由图可知,当输入信号频率在fr附近有较大输出时,这显示了数字互相关检测的频率选择性;但当输入信号频率在fs±fr附近也有较大输出时,这是由于信号频率大于折叠频率fs/2而产生了混迭效应。

混迭效应会使数字LIA的频率选择性能变差,实际中应在对信号采样前使用反混迭低通滤波器,将大于折叠频率的成分滤除。下面只考虑信号频率不大于折叠频率的情形,即a在[0,N/2]内,取值分析式(6,7)可以得出下列结论:

(1)如a=k/q,k为整数且k≠q,有Rxrs=Rxrc=0,由此可知对于非1次的谐波信号,输出完全无响应。

(2)在a>1+1/q时,随a的增大,Rxrs和Rxrc呈振荡衰减趋势,在a<1-1/q时,随a的减小,Rxrs和Rxrc呈振荡衰减趋势;在a∈[1-1/q,1+1/q]时,Rxrs,Rxrc取值较明显,即当f在[fr-fr/q,fr+fr/q]频带范围内时输出较大,此频带宽度为2fr/q=2/qTr=2/Tc,Tc=qTr是测量时间。

3 数字LIA的实现

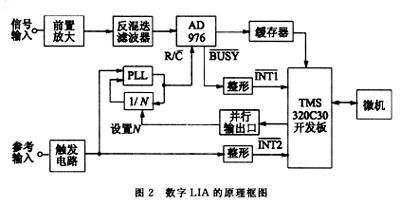

实际设计了一个使用TMS320C30 DSP和采样ADCAD976的数字LIA,TMS320C30是速度快、功能强、使用方便的32位浮点运算DSP,AD976是最高采样速率为100 kHz的16位并行ADC。图2给出了数字LIA的原理框图,系统由信号处理电路、TMS320C30开发板和微机组成。此数字LIA使用起来相当方便、灵活,DSP执行的程序由微机来加载,DSP计算得到的结果传送给微机来显示和存储。

下面对图2所示数字LIA的主要工作过程作简要说明。一个方波或其他形式的周期信号连接到系统的参考输入端,通过触发电路得到TTL电平的方波信号,再经过整形电路产生约100 ns的脉冲和DSP的INT2相连,使DSP可靠地产生一次中断,首先DSP要用内部定时器来测量响应两次中断INT2的时间间隔,由此可得参考信号的周期Tr和频率fr。当fr在10 Hz~30 kHz范围内时,由DSP计算90 kHz除以fr的商值并以所得结果的整数部分作为N值,通过并行输出口将锁相环(PLL)倍频电路中的分频器设置为N分频,显然N在3~9 000范围内取值,采样频率在67.5~90 kHz范围内取值。AD976的转换结束信号经过整形电路产生约100ns脉冲,此脉冲和DSP的INT1相连,DSP在响应某一此中断INT2后允许响应中断INT1,这实际上是通过参考信号来确定起始采样。DSP响应中断INT1进行实时处理,读入采样所得数据并转换成浮点数,计算出对应这一采样点的数字正弦、余弦参考信号,然后进行互相关的相乘、累加操作,在采样M次后将得到的累加值除以M得到最后的互相关运算结果。这里,在存储器中预先装入了[0,2π]区间内1 024个等分数据点的正弦、余弦值,DSP通过计算正弦、余弦函数在某一数据点的三阶泰勒多项式,可以快速获得所需的数字正弦、余弦参考信号。

- TI低成本、高性能家用与车载音频 DSP (05-27)

- 基于MSP430的直流宽带放大器设计(07-09)

- 集成方式用于解决混合信号半导体的挑战(08-27)

- 一款基于单片机的脉冲快速充电系统设计(06-28)

- 使用基于PXI的仪器和高速流盘技术进行下一代射电天文接收机算法原型开发(09-08)

- 藏在系统核心芯片中的DRAM控制器(12-10)