基于ADSP-TS201S的多DSP并行系统

,在设计中采用PCI9656作为CPCI接口芯片。PCI9656作为专门 的I/O加速器,支持CPCI格式传输,数据传输时钟主频最高为66 MHz,数据传输带宽为64 b。其峰值传输速率可达528 MB/s,通过系统框图可以看到,在设计中使用了CPCI的J1,J2,J3,J4四个接口,根据CPCI传输协议,J1和J2为64位PCI数据传输接 口。J3,J4为自定义方式接口,设计中定义J3为处理板和后面板的数据传输接口,J4为上下处理板间的数据传输接口。

4.4 外部设备接口设计

本系统通过公用总线连接的存储器资源有:4个扩展应用的SDRAM,2个FLASH,2对扩展应用的FIFO,以及DSP片内存储器资源。所有存储器资源都通过统一的地址空间映射来进行区分。ADSP-TS201S的32位地址总线提供了高达4 GB的寻址空间,可以划分为4部分:

(1)主机寻址空间。地址映射范围0X80000000~0XFFFFFFFF,用于片外主机接口的地址映射空间。

(2)外部存储块空间。地址映射范围0X30000000~0X7FFFFFFF,用于处理器外围设备存储器接口地址空间映射,包括通用的存储器设备和SDRAM存储器。设计中主要对此空间进行划分,为外部存储器分配单独和惟一的地址空间。

(3)多处理器空间。地址映射范围0XOC000000~0X2FFFFFFF,主要用于多处理器构成的系统各个处理器间相互共享内部存储空间映射。

(4)片内存储空间。地址映射范围0X00000000~0X03FFFFFF,定义内部存储器空间映射。

外部存储器可以分为SDRAM寻址空间和外部通用存储空间。设计中,扩展连接的SDRAM将分配占用SDRAM寻址空间,而外部FLASH和FIFO将分配占用通用存储空间。

每两片SDRAM扩展连接为64位形式,设计用MSSD0和MSSDl分别作为每两片SDRAM的共用片选信号的控制信号,对应SDRAM寻址空间为0X4000 0000~0X44000000和0X50000000~OX54000000,可以分别获得128 MB的存储器寻址范围,满足SDRAM寻址要求。

外部两片FLASH的寻址空间划分分别通过MS0_AB与BMS_AB和MS0_CD与BMS_CD这两组信号作为片选信号,分配寻址空间为0X30000000~0X34 000000和0X34000000~0X348000000,寻址空间范围为128 MB。

外部4片FIFO,每两片扩展接成32位输出/输入方式,在进行地址映射时,实际上可以映射到一个地址寻址空间,而通过控制读写信号来进行区分,使用 MSl信号作为FIFO使能信号,获得分配的寻址空间0X38000000~0X40000000。为方便逻辑控制,MS1信号脚连接到FPGA上,通过 FPGA的逻辑译码来获得对FIFO的寻址控制。

另外,将ADSP TS201S的高八位地址线也连接到FPGA上,通过逻辑译码进一步可以获得较为细致的地址划分方案,为设计带来更多的灵活性,同时也确保了设计的可靠性。

5 系统软件设计

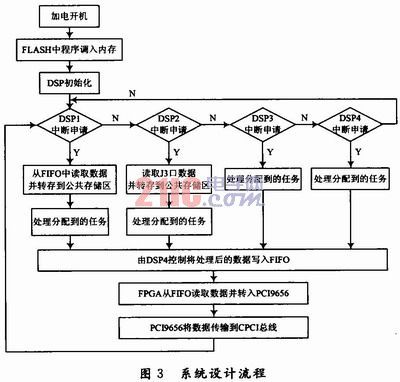

由于系统硬件是基于DSP+FPGA的结构,相应的软件也分为两个功能模块。FPGA主要完成整个系统的数据传输逻辑控制,因此FPGA具体的处理流程嵌套在DSP的信号处理流程中。4片DSP主要完成信号的处理,大致的系统设计流程如图3所示。

4片DSP并行工作时,总线仲裁策略指定DSPl为主处理器,由它完成系统的初始化、数据程序配置、与CPCI工控机主机通信等,并参与运算工作。当系统 接收到数据时,首先判断信号的传输方式,若是并行信号,由FPGA进行相应处理后写入FIFO中,同时通过外部中断告知DPS-l,随即DSPl发出中断 申请,总线仲裁令DSP1获得总线控制权,读取FIFO中的数据并转存至公共存储区;然后DSP1通过LINK口与其他DSP通信,进行任务分配,其他 DSP依次循环获得总线控制权,读取数据进行处理然后再存入存储区;最后,由DSP4控制将存储区里的数据写入FIF-O,同时通知FPGA读取并完成时 序转换后传输到PCI9656,由PCI9656将数据传输到CPCI总线,完成这一帧数据的处理。若系统接收到的数据是由J3口传输来的串行信号,则先 由DSP2发出中断申请,总线仲裁令DSP2获得总线控制权,将接收到的数据转存至公共存储区;然后通过同样的方式在4片DSP间进行任务分配和处理,由 DSP4写入FIFO,最后由FPGA和PCI9656联合将数据传输到CPCI总线,完成串行信号的处理。

6 结语

本文介绍了一种基于PFGA的多DSP并行处理系统的设计,重点对DSP并行结构设计进行了分析,并介绍了FPGA设计和外部设备接口设计。实际应用表 明,该多DSP并行处理系统应用于宽带雷达信号处理时,能够满足任务中的各项指标,还能完成设计外的其他功能,并且易于控制,稳定可靠。本文提供的系统设 计方案能够为处理宽带雷达信号的其他研究人员提供一定的参考。

ADSP-TS201S 多DSP 并行系统 相关文章:

- 基于ADSP-TS201S的二维DMA数据传输(03-08)

- 基于多DSP并行处理的声探测系统设计(02-10)

- 高性能多DSP互连技术研究(01-28)

- 基于高性能多DSP互连技术研究(04-02)

- 基于FPDP和VME总线的多DSP通用并行处理系统设计方案(04-07)

- 基于ISA总线的通用多DSP目标系统设计(05-07)