基于DSP和CPLD的低压断路器智能控制系统的设计

0 引言

智能电网的发展,对低压电器的智能化提出了较高的要求,目前国内使用较多的小型断路器的智能化稳定性不够,在于其体积较小,将信号采集电路、动作执行和智能脱扣器都安装在本体内,开关内的强电场产生的电磁干扰和高温,使得断路器可靠性降低。本文介绍的智能控制器脱离于断路器本体,并且能够连接多个断路器,实现对多个断路器的监控。

1 控制器的总体结构

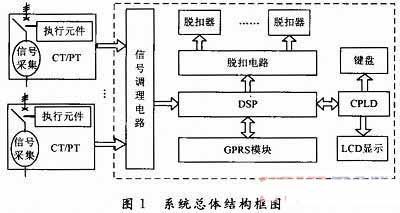

群组智能控制器的核心采用DSP TMS320F2812芯片,辅以CPLD EPM3128芯片来实现键盘和液晶的时序逻辑,减少扩展芯片带来的体积问题,外围电路主要包括信号调理电路和脱扣控制电路等。为适应智能电网的无线通信,在智能控制器中添加GPRS模块,使得断路器能够更好地融入到智能电网中。

2 控制器的硬件设计

所采集的多个断路器的电压、电流等信号,经过信号调理电路进行调理后送入DSP处理器,经过信号的变换、运算和判断等处理,断路器有故障时通过脱扣电路实现脱扣。系统总体结构框图如图1所示。

2.1 信号调理电路模块设计

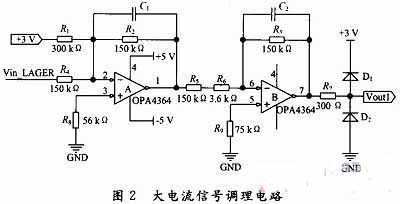

信号调理模块的主要功能,一是低通滤波,滤除高频噪声;二是信号放大,由于检测电流范围较大,为适应较大的动态范围,提高A/D采样分辨率,使变换后的数字信号尽可能准确反映模拟信号的大小,设计了两路放大环节。一路有较大的放大倍数,放大小电流时的信号;另一路放大倍数较小,进行大电流时的信号放大。因为A/D转换器的信号输入范围有限,为防止大电流信号时产生过高的输入电压,对检测电路和A/D转换器造成损坏,设计了电平限幅保护电路。

图2为每一相大电流信号滤波、平移、放大和限幅电路。由于A/D转换器输入电压范围为0~3 V;而输入信号是直流偏移电平为0 V的交变正弦波,所以设计电平偏移电路抬高电流信号。低通滤波和信号放大由两级运放组成。

2.2 脱扣电路模块设计

脱扣电路分为数字脱扣与模拟脱扣数字脱扣电路较为简单,DSP通过I/O口输出脱扣信号,经过光耦隔离放大驱动磁通线圈。模拟脱扣电路采用比较器电平鉴幅电路实现,每一相电流采用两个比较器来完成,当微处理器没有发出脱扣信号且电流信号的幅值在参考基准电压范围内,则比较器并联输出一高电平,否则为低电平。低电平信号通过脉宽检测电路,进行抗干扰处理。如果低脉冲维持一定的宽度则单稳态触发器被触发,同时输出一定宽度的脉冲通过驱动电路使磁通变换器打开,从而分断断路器。模拟脱扣电路如图3所示。

比较器电平鉴幅电路在实际应用中,由于干扰的存在,比较器的输出会出现一些不必要的窄脉冲,因此设计了脉宽检测电路用于滤除干扰尖峰引起误触发脱扣动作。在设计时,当输入脉冲宽度大于1ms时,输出32.9ms的脱扣信号;当小于1ms时,不输出脱扣信号。

模拟脱扣电路在实际应用中,上电初期的短路电流只在100 ms内起作用,其后即在DSP初始化完毕开始正常运行,模拟脱扣电路则进行特大短路电流的判断,两种不同情况,其电流定值不同。因此设计了可切换参考基准电压,即MCR分断接通电路。MCR分断接通电路在上电初期,C408两端电压较低,通过比较器输出高电平,使得T401饱和导通,因此参考基准电压降低,即模拟脱扣动作值较低,出现短路故障时,实现MCR脱扣。上电稳定后,C408两端电压升高,通过比较器输出低电平,使得T401截止,此时参考基准电压较高,在出现特大短路电流时,实现模拟脱扣,MCR脱扣电路如图4所示。

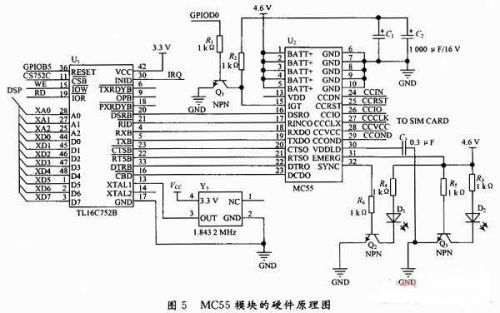

2.3 GPRS通信模块与DSP硬件接口设计

GPRS通信模块采用SIEMENS公司的MC55GPRS模块,软件原理图如图5所示。DSP芯片F2812通过外部总线接口XINTF扩展了一块带双异步串口(UART)的TL16C752B芯片,和MC55 GPRS模块相连。DSP芯片主要实现整个系统所需的协议以及监测数据的采集、中心主站的命令的解析;GPRS模块则完成无线通信功能。

3 控制器软件设计

系统软件主要完成信号采样,脱扣算法,通信处理和按键显示等功能。控制器的软件设计采用汇编语言和C语言混合编程的方法进行程序结构优化,以确保实时性。程序具有模块化和子程序化的特点,同时在程序设计中加入了抗干扰处理。主程序流程图如图6所示。

4 结语

本文详细叙述了智能控制器系统各组成部分的设计过程,并给出了具体的电路图。通过软件与硬件系统测试表明,该智能控制器能够较好地完成信号采集、无线通信和线路通断控制功能。在后续的研究中,可采用嵌入式实时多任务操作系统μC/OS-Ⅱ作为系统软件平台,实现μC/OS-Ⅱ在F2812上的移植。

- 在采用FPGA设计DSP系统中仿真的重要性 (06-21)

- 基于 DSP Builder的FIR滤波器的设计与实现(06-21)

- 达芬奇数字媒体片上系统的架构和Linux启动过程(06-02)

- FPGA的DSP性能揭秘(06-16)

- 用CPLD实现DSP与PLX9054之间的连接(07-23)

- DSP+FPGA结构在雷达模拟系统中的应用(01-02)