基于DSP的近距离无线通信的嵌入式数据记录设备设计

寄存器,通常只需设置"配置选择寄存器"以选择CF卡的读写模式。CF卡的读写模式有3种:I/O模式、Memory模式和True IDE模式。本设计使用16位的Memory模式读写CF卡。Memory模式是CF卡默认的读写模式,所以在CF卡初始化过程中不需要设置"配置属性寄存器"。

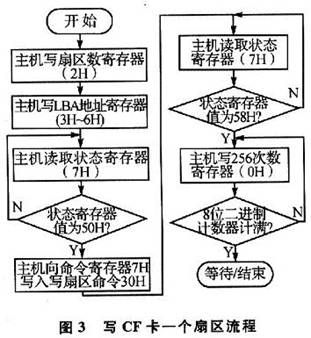

其次,设置CF卡的任务文件寄存器。本设计中使用的任务文件寄存器有:数据寄存器、扇区数寄存器、扇区号寄存器、低柱面号寄存器、高柱面号寄存器、驱动器选择/磁头寄存器和状态/命令寄存器。对它们进行没置,可选择扇区寻址方式,设定每次读写的扇区数和逻辑寻址地址,并获取CF卡状态以及输入读写命令。

CF卡的寻址方式与计算机的硬盘操作方式类似。扇区的寻址方式有两种:物理寻址方式(CHS)和逻辑寻址方式(LBA)。本设计使用LBA寻址,对应28位LBA地址。

磁头寄存器存放LBA地址的27~24位;柱面号寄存器存放LBA地址的23~8位;扇区号寄存器存放LBA地址的7~0位。

写CF卡一个扇区的流程如图3所示。每次向CF卡存储数据时,应该先获取上次存储到的扇区的LBA地址,从而获得此次存储的起始扇区地址。为了记录每次存储到的扇区的地址,将LBA地址为0的扇区保留,专用于记录扇区地址。在开始一次写操作之前,应该先读取LBA地址为O的扇区,获得上次存储的LBA地址;然后加1获得此次写操作的LBA地址,并向指定的扇区写数据。

利用QuartusII作为FPGA开发平台,使用VHDL硬件描述语言实现了FPGA与DSP的接口、异步FIFO的存储以及CF卡的读写逻辑。在QuartusII自带仿真工具下得到的写CF卡时序仿真结果如图4所示。

3.2 无线通信模块设计

3.2.1 蓝牙模块设计

蓝牙模块采用BTM0604C2P。它内嵌蓝牙芯片BlueCore4-Ext,兼容蓝牙2.0+EDR规范,最高支持3 Mbps的数据速率,外置天线,有效距离为10 m,具有标准的UART接口。

DSP与蓝牙模块之间通过HCI协议层建立连接。HCI(Host Controller InteRFace,主机控制器接口)协议,为DSP提供了一个访问蓝牙模块内部基带控制器和链路管理器的命令接口,可以获取蓝牙芯片的配置参数。

本设计中,DSP和蓝牙模块之间采用UART方式进行通信。DSP使用的控制信号除了异步串行通信收发信号SCIRXD和SCITXD外,还有4个控制信号,分别与蓝牙模块的LNK、CLR、RTS和CTS引脚相连。其中,LNK脚用于指示蓝牙主机和从机连接是否建立,地面设备PC机为蓝牙主机,DSP作为蓝牙从机;CLR脚用于切换蓝牙模块的工作模式,包括参数设置模式和数据传输模式;RTS和CTS脚为"请求发送"和"清除发送"引脚,用于实现DSP和蓝牙模块之间的对话,使数据正常传输。

蓝牙模块的SLEEP引脚,既可以使蓝牙模块在休眠和唤醒状态间切换,也可以用于清除蓝牙模块内嵌芯片记忆的配对主机地址。这些功能的实现由按键控制,通过区别按键的时长加以区分所需实现的功能。蓝牙模块的复位信号RESET输入低电平脉冲时有效,而且要求脉冲宽度大于5 ms。

3.2.2 红外模块设计

红外模块采用HP公司的红外收发器芯片HSDL_1001和红外编解码器芯片HSDL_7001,二者均遵循IrDA 1.O协议。红外信号的收发使用PWM方案,采用RZI编码调制解调,调制脉冲宽度为3/16位,调制频率为38 kHz。由于硬件接口的限制,嵌入式系统中红外通信的速率为9 600~ll5200 bps。红外数据的传输以帧为基本单位,传输过程中采用1 6位的CRC码进行数据校验。

系统采用Maxim公司的芯片MAX3110作为DSP的SPI接口和HSDL_7001的UART接口之间的转换芯片。MAX3110和HSDL_7001均使用外部无缘晶体振荡电路供电,所用的晶振大小分别为1.843 2 MHz和3.686 4 MHz。需要下载的数据,首先经过红外编解码器编码,再通过红外收发器上集成的发光二极管以红外光信号的形式向PC机发送。

4 系统软件设计

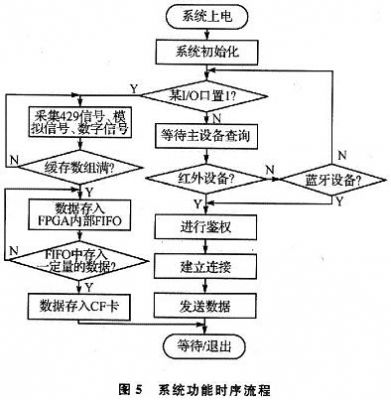

系统的功能时序流程如图5所示。DSP部分程序用C语言编写,结合硬件电路对数据采集、数据传输进行处理和控制。主要的中断应用有ARlNC429信号采集中断和红外通信请求中断。系统的工作流程以时序控制流程为主线。系统初始化之后,进行任务选择与执行。若特定的I/O口置1,则进入数据存储程序,采集数据并存至CF卡;若I/O口置O,则进入数据下载程序,等待主设备的连接请求,鉴权并建立相应的连接,读取CF卡数据,并通过无线通信模块向主设备发送。

结语

本文根据某工业现场电子设备的特殊应用需求,提出了一种基于无线通信技术的数据记录系统。该系统利用DSP与FPGA协同控制方式实现数据的采集和存储,利用红外和蓝牙模块实现数据的无线下载;用红外和蓝牙代替有线线缆和插拔存储卡等传统数据下载方式,操作方便,避免了传统方式可能造

- 在采用FPGA设计DSP系统中仿真的重要性 (06-21)

- 基于 DSP Builder的FIR滤波器的设计与实现(06-21)

- 达芬奇数字媒体片上系统的架构和Linux启动过程(06-02)

- FPGA的DSP性能揭秘(06-16)

- 用CPLD实现DSP与PLX9054之间的连接(07-23)

- DSP+FPGA结构在雷达模拟系统中的应用(01-02)