基于GIO/FVID的DSP视频系统设计

3.2 视频处理程序运行流程

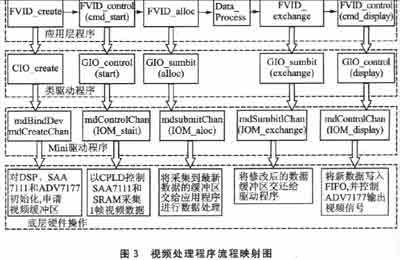

在设计完成的视频驱动程序基础上,开发一个典型的视频处理应用程序,其运行流程如图3所示。首先使用FVID_create函数建立GIO_capture和GIO_play两个视频通道.再以GIO_capture通道的FVID_control函数发出cmd_start,采集到1帧视频数据。应用程序以GIO_capture通道的FVID_alloc函数向驱动程序申请采集到的数据帧,进行处理后再以FVID_exchange函数将修改后的数据帧返回驱动程序,最后再调用GI0_play通道的FVID_control函数发出cmd_display命令将数据帧输出。由图3可以看到,应用程序调用的这些FVID_XXX接口函数会自动由类驱动程序层层向下映射,到达迷你驱动层程序;而迷你层程序可以直接操纵底层硬件设备,来完成整个视频的采集、处理和显示的过程。

3.3 迷你驱动程序的设计

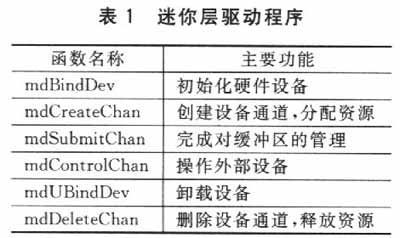

迷你层驱动程序足整个设计的重点所在,下面详细介绍其实现方法。迷你层驱动程序主要由表1所列的几个函数组成。

对各个函数的具体实现如下:

①mdBindDev函数。在应用程序建立设备接口(如FVID_create函数)时被调用,完成对外部设备的初始化。而与其对应的是md_UBindDev函数,使用nadUBindDev函数会使设备处于无效状态,不能再使用。

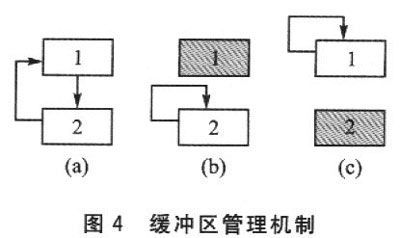

②mdCreateChan函数。使用此函数为应用程序和驱动程序建立通信通道,同时为每个通道申请缓冲区。在TI公司发布的FVID模型中,为每个通道都分配了3个缓冲区,轮流与外部设备交换数据,每个缓冲区对应1帧视频数据,这样的设计在DM642这样可以外扩大容量SDRAM的系统中是完全可行的。但是对于本系统,F2812DSP外部只扩展了512K×16位的SRAM,既要做视频输入的帧缓存,义要存放一部分程序,这样存储空间就不够了。所以本设计中进行了简化,对视频输入设备采用两缓冲区轮转的机制,如图4(a)所示。而对于视频输出设备,以AL422 FIFO作为硬件帧缓存,而不在SRAM中再为其分配缓冲区。与mdCreateChan对应的是md-DeleteChan函数,用于删除设备通道,释放缓冲区资源。

③mdSubmitChan函数。负责管理缓冲区。分别接受应用程序发出的FVID_ALLOC、FVID_EXCHANGE、FVID_FREE三个命令并进行处理。其中FVID_ALLOC命令对应图4中(a)到(b)的过程,应用程序从两个缓冲区中取出最新的一帧视颧数据,埘其中的数据做处理,而只剩下一个缓冲区用来接受外部设备输入的数据。FVID_EXCHANGE对应图4中(b)到(c)的过程,应用程序处理完1帧数据,将这1帧数据返回驱动程序,准备用来显示,同时再读入新的l帧数据进行处理。FVID_FREE对应图4中(c)到(a)的过程,应用程序将处理完的数据帧返回驱动程序,而不再向驱动程序申请新的数据帧。以上3个命令足针对视频输入接口GIO_capture而言的,而对于输出设备接口GIO_play,在SRAM中没有分配缓冲区,所以其nldSubmitChan函数内部设为空函数。

④mdControlChan函数。用来操作外部视频设备,完成对视频数据的采集和输出。对于GIO_capture和GIO_play这两个设备接口的mdControlChan函数接受的命令是不同的:

视频输入GIO_capture接口的mdControlCham函数只接受cmd_start命令,完成1帧视频数据的采集;而视频输出GIO_play接口的mdControlChan函数只接受cmd_display命令.完成视频信号的输出。

3.4 视频驱动模型裁剪的一般方法

TI公司设计的GIO/FVID视频设备驱动原型相对复杂,且占用较多的系统资源,要使其可以应用于更通用的低端处理器系统,就必须进行改造和裁减。在改造中要注意以下几个方面:

①阻塞的I/0操作。TI公司6000系列的DSP具有FDMA功能,传输数据不需要CPU的干预,而DM64X还具有专用的视频接口,传输数据不会占用外部扩展总线,所以视频数据的处理和输入输出是可以并行的。而低端处理器是不具备这样功能的,视频设备一般都是通过外部扩展总线连接的,所以对视频设备的操作必须设计为阻塞型的I/O操作,视频数据输入/输出的过程是由CPU来完成,且要保证对视频设备的操作不会被其他操作中断。

②对视频数据缓冲区的管理。GIO/FVID视频设备驱动原型中使用的3缓冲区模型,虽然功能很完善,却占用了太多的存储空间,所以对于实际的视频处理系统就要进行调整,改为两缓冲区甚至是单缓冲区模型。对于具有独立硬件缓存的输出设备,可以考虑不再为其分配动态缓冲区。

③对视频设备的操作。mdControlChan函数主要用来操作外部视频设备,只要保留对实际系统有用的操作就足够了,而GI0/FVID视频设备驱动原犁中定义的很多操作都可以省略。

4、小结

本文介绍了基于DSP/BIOS的外设驱动程序模型,并针对基于F2812DSP的视频处理系统这一具体的硬件平台,重点介绍了开发GIO/FVID设备驱动的流程和针对低端处理器系统的视频驱动模型裁减方法。本视频驱动程序为开发各种视频处理应用程序(如JPEG图像EPA控制网络中ZigBee压缩、MPEG视频压缩、视频监控程序等)提供了有力的支持。本文介绍的设备驱动程序的开发方法,对于同类视频处理系统,特别是对于使用TI2000系州DSP这样系统资源比较有限的视频处理系统,具有很好的可借鉴性。

- 在采用FPGA设计DSP系统中仿真的重要性 (06-21)

- 基于 DSP Builder的FIR滤波器的设计与实现(06-21)

- 达芬奇数字媒体片上系统的架构和Linux启动过程(06-02)

- FPGA的DSP性能揭秘(06-16)

- 用CPLD实现DSP与PLX9054之间的连接(07-23)

- DSP+FPGA结构在雷达模拟系统中的应用(01-02)