DSP在心电工作站的应用

1 引 言

目前,以心电信号自动测量、分析和诊断为主的心电工作站系统已经得到了广泛的应用,对于心脏疾病的早期预防、实时诊断发挥了较大的作用。分析传统的心电工作站系统,可以发现如下的特点:1)大多是基于PC机系统,心电信号经PC采样接口卡存储到PC上,然后由PC机进行分析处理,这在一些场合(如病人床边、家中)的数据采集时使用不方便;2)由单片机做成体积小、可以随身携带的仪器,但是,由于目前8/16位的单片机系统运算能力有限,而且数据空间有限,对于一些长时间的数据采集或要求较复杂算法的信号处理就无能为力了。

如何将PC系统的大数据空间、高运算能力与单片机的小型化结合起来,DSP器件提供了良好的解决方案。DSP器件是为数字信号处理设计的高性能处理器件,已经在通讯、图像处理、医疗等诸多领域得到了广泛的应用,而且随着大规模集成电路技术的发展,其性价比比也有很大的提高。本文介绍一种以 DSPTMS320C32芯片为核心的心电信号实时采集系统。

2 系统结构

2.1 TMS320C32特点

TMS320C32是美国TI公司浮点C3X系列DSP器件的新一代产品,它针对C30和C31进行了简化和改进,具有如下的特点:

1)外接40 MHz的晶振,具有40 MFLOPS,20MIPS的运算速度,32位运算精度,强大的指令系统,所有指令单周期执行;

2)丰富的硬件资源,包括1个串行口,两个时钟,两个DMA控制信道,优先级可以设置,4级优先中断,支持多种的寻址方式,提高了信号处理的运算能力;

3)较大的寻址空间,24根地址线有近16 Mb的空间,数据程序总线的宽度可变,STRB0、1可定义为8/16/32位的数据宽度和外部存储器宽度;

4)外部中断触发方式可选电平/边沿方式,内部中断矢量表地址可复位,程序引导可由芯片内部Boot Loader实现;

5)增加了两种节电运行方式,低功耗。

2.2 系统主要设计指标

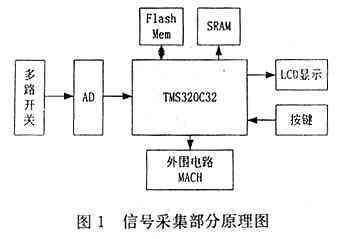

下面是以DSP为核心的心电数据采集系统的设计框图,如图1所示,主要包括以下特点:

1)多通路信号采样,可控制模拟多路开关采集16路信号,包括12路常规心电信号ECG、3路正交信号CMP和1路心率变异信号HRV;

2)A/D采样频率为16 kHz,分辩率为12 bit,转换精度高,线性误差为1/2 LSB;

3)大存储容量。1 Mb的存储空间,能够存储多路长时心电数据及分析诊断结果;

4)有可编程逻辑芯片MACH实现逻辑控制;

5)其它部分,包括LCD图形点阵式液晶显示、输入按键。

2.3 信号采集系统

2.3.1 程序及数据存储器

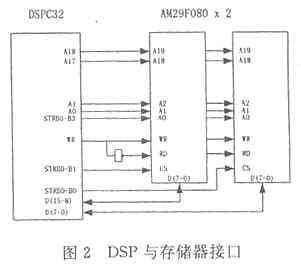

多路心电信号实时采集的数据量比较大,10 s的常规12路ECG信号有240 k字节的数据量。系统选用大容量的快速闪存作为存储器。C32允许可变宽度的外部存储器接口,用作数据存储时,宽度可以是8/16/32位,用作程序存储时,宽度可以是16/32位,因此,设计16位的外部存储器接口,同时用于存放应用程序和数据,两片Atmel27F080构成1Mb×16的存储器,采用16位的存储器接口方式,减小了系统的体积。Atmel 27F080的数据存储时间是70 ns,符合快速接口的要求,允许任意位置数据的存储、擦除,与DSP的连接如图2所示。

DSPC32的内部RAM是512字,为增强其算法处理能力,外部扩展了32 kb的高速SRAM,由4片ISSI61C256-15构成,其存储速度是15 ns。

2.3.2 多路开关和A/D信号采集

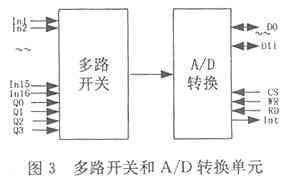

经放大后的多路心电信号通过多路模拟开关后输入到A/D转换器,进行时分多路的信号采样。多路开关选用Max336 16路选1的开关。设计信道1~12用作12路常规心电信号输入,信道13~15用作3路正交信号的采集,信道16用作心率变异信号输入。具体采集时由DSP控制逻辑器件确定所要采集的通路。

A/D转换由Max196完成。Max196能实现12bit模数转换,单5 V供电,内部有参考电压Vref转换电路,支持±10 V、±5 V、0~10 V、0~5 V的电压转换范围,由控制字确定输入信号的范围,A/D转换的速率可达100 ksps,具有低功耗的工作方式,输入输出引脚全部三态,与微处理器的接口简便,如图3所示。

DSP往其写控制字启动A/D转换,A/D转换结束后,产生Int信号,连到DSP的Int1上,产生外部中断,DSP读取转换结果。系统的采样频率是16k,DSP的指令周期是50 ns,因此,在两次转换的间期,DSP有充足的时间进行数据处理,包括数据滤波、存储等。

- 基于AT89C52的电化学工作站设计(12-06)

- TMS320C32芯片的工作站系统原理及结构(06-06)

- 在采用FPGA设计DSP系统中仿真的重要性 (06-21)

- 基于 DSP Builder的FIR滤波器的设计与实现(06-21)

- 达芬奇数字媒体片上系统的架构和Linux启动过程(06-02)

- FPGA的DSP性能揭秘(06-16)