CPLD在DSP系统中的应用设计

辑处理,达不到延时的效果。所以采用高频时钟驱动一移位寄存器,对移位寄存器进行正确的设置后,输出即为延时后的数据。语句如下:

always@(posedge eclkout2) //采用dsp的clkout=100MHz 二分频后作延时

begin

if(svs_rst_) //svs_rst_低电平,count始终置1010

begin

count=4'b1010;

end

else if(count==4'b0000) //0000则保持

begin

count=4'b0000;

end //svs_rst_高电平,count

开始计数

else

begin

count=count+4'b0001; //记六次至0000

end

end

assign tp4=count[3];

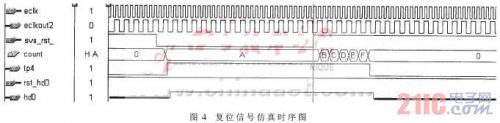

仿真效果如图4所示。由仿真波形可见,CPLD的信号输出完全符合DSP BOOT 的两个要求。

2.3 HPI口接口逻辑的实现

图像压缩编码器通过DSP的 HPI口与网络模块连接,实现图像的网络传输。TMS320C6202的HPI口是指其扩展总线的主机口接口部分。经过编码器编码后的MPEG-4图像数据以帧为单位存放在DSP内部存储器中,外部主机通过HPI口读取。现以MCF5272微处理器与HPI口通信为例进行说明。

MCF5272将10/100MB以太网控制器和一个USB模块等通信外围设备结合起来, 是一款高集成的ColdFire微处理器。详见参考文献[4]。

MCF5272与TMS320C6202连接采用异步从属工作方式,MCF5272作为上行机,TMS320C6202作为从属机。由MCF5272高位地址线模拟XCNL、XR_W信号,TMS320C6202的多功能串行口3工作在GPIO模式下模拟信号,为MCF5272提供主机口中断。本系统由CPLD--MAX7000编程实现两者硬件接口。仿真后的时序如图5所示,实验证明可以满足双方时序要求,实现数据传输。

以上所讨论的逻辑并不复杂,采用74系列在一定程度上说也可以完成。但是,采用CPLD具有以下优势:体系结构和逻辑单元灵活、集成度高、适用范围广,因而采用CPLD的方案。

在开发阶段,通过硬件实现的控制信号往往不能确定,需要试验验证。而CPLD因其具有灵活性,逐渐成为DSP进行信号处理不可或缺的协处理器。将相关控制信号接入CPLD,只需通过简单的编程即可实现各种需要的逻辑,避免了硬件上的改动,使硬件逻辑控制更加方便灵活,对类似设计具有普遍意义。文中讨论的防抖动以及CPLD延时程序对于类似设计也有一定的借鉴意义。

本文介绍的CPLD在基于DSP的MPEG-4编码压缩模块的系统中的应用实例,已通过下载验证。应用在工程实践中,结果表明该设计是方便灵活且正确有效的。

RESET Boot HPI CPLD的延时 时序 相关文章:

- Reset与嵌入式系统应用的稳定性(01-09)

- VxWorks中怎么从Flash BOOT(11-15)

- U-Boot的编译与移植到QT-S3C44B0X开发板上(03-08)

- WinCE系统下BootLoader的开发(04-10)

- 嵌入式linux启动信息完全注释(04-24)

- 基于S3C2410A的嵌入式系统的U-Boot移植(01-24)