Reset与嵌入式系统应用的稳定性

嵌入式系统的应用领域越来越广泛,干扰或者恶劣环境常影响嵌入式系统运行的稳定性和可靠性。Reset是维护系统稳定的一个关键因素,正确地设计复位电路,巧妙地应用复位操作,能使整个系统更可靠、稳定地运行。本文结合实际项目经验分析Reset的相关应用与设计,展示Reset对系统稳定性的重要性。

引言

在嵌入式系统电子设备的运行中,当出现程序跑飞的情况或程序跳转时,可用手动或自动的方法发信号给硬件特定接口,使软件的运行恢复到特定的程序段运行,这一操作就是复位(Reset);这一过程中,手动或自动发给硬件特定接口的信号,就是复位信号。为了克服系统由于内因(时钟振荡源的稳定性)和外因(射频干扰)所引起的运行不稳定的情况,在嵌入式系统软件和硬件上,必须作相应的处理和保护。复位操作是一种行之有效的保护措施,同时复位系统本身也是引起嵌入式系统运行不稳定的因素,在设计时需特别注意。

本文结合笔者亲身经历的实例来说明Reset的重要性,巧妙地运用Reset使系统工作更稳定可靠。

1 Reset方式及手段

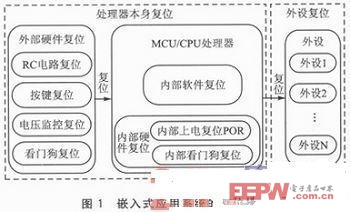

在嵌入式应用系统中,复位操作包括两个方面——处理器本身的复位和系统中外设(外接功能模块)的复位,如图1所示。

总的说来,嵌入式复位方式主要分硬件复位和软件复位。硬件复位,即采用硬件的手段、通过硬件复位信号对系统处理器或者外设进行复位。只要在RST端出现一定时间(具体看系统和处理器的机器周期)的复位电平信号,由CPU采样复位信号,启动复位时序,即可完成复位操作。硬件复位一般包括上电复位、按键复位、电压监控复位和看门狗复位等,这些复位信号,在系统设计时可用逻辑电路组合起来加载到系统的RST端。软件复位,即通过软件手段,在软件框架里对系统复位,重新初始化系统。

按处理器内外来划分,又分为芯片内复位和芯片外复位。于是,硬件复位又分外部硬件复位和内部硬件复位。

对于硬件复位,按复位信号电平高低又可分为高电平复位和低电平复位。高电平复位是高电平有效,并在复位脉冲的下降沿完成复位过程;低电平复位是低电平有效,并在复位脉冲的上升沿完成复位。具体用什么复位信号,视嵌入式系统本身而定,但大多采用低电平复位,这与TTL的功耗有关,因为TTL电路中高电平的吸收电流要远小于低电平的吸收电流。

2上电复位的实现及稳定性设计

2.1上电复位

上电复位(Power On Reset,POR),即系统上电时通过复位电路,在RST引脚提供一个足够长时间的复位电平信号,直至系统电源稳定后,再撤销复位电平。在嵌入式系统中,上电复位是系统启动初始化复位,全面而系统地复位处理器内的所有逻辑单元与模块,将初始化内部逻辑操作,如存储器控制器、中断控制器和I/O引脚等的配置。

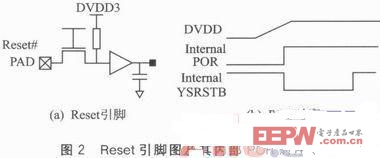

上电复位是保证嵌入式系统正常运行的基本操作。通常处理器芯片内部自带上电复位电路,图2(a)所示为某MCU(微控制器)Reset引脚示意图,内部自带上电复位电路。MCU芯片上电时,片内POR将产生内部复位信号以初始化芯片内的数字模块,其时序如图2(b)所示。

有的处理器芯片通过在片外添加RC延时电路来得到上电复位信号。RC复位电路的复位脉冲宽度由芯片要求的复位时间决定,持续时间取决于RC电路参数,电容太大复位时间很长,电容太小复位时间不够,不足以稳定复位。

2.2上电复位失效及应对措施

实际工作时,由于各方面的原因,上电复位会失效。由于受到干扰、电源波动、误操作等原因,短暂的电压下降造成供电恢复时由于电压没有满足POR的发生条件,复位端的低电平复位信号无法再次启动系统重新复位工作,此时会出现系统死机;电源二次开关时间间隔太短时,复位不可靠;当电源电压中有浪涌现象时,可能在浪涌消失后不能产生复位脉冲。这些现象尽管并不频繁,但对于某些特殊应用场景,如不能随时进行手动复位的远程自动控制系统,却是致命的。

出现失效时,常采用提高复位门限来应对,使复位门限位于处理器正常工作电压范围内,且接近处理器正常工作时的最低门限。另一应对措施是延长复位信号时间,让复位信号在电压值恢复后维持足够长的时间。电源稳定后还要经过一定的延时才撤销复位信号,以防止电源开关或电源捕头分一合过程中引起的抖动影响复位。另外,为了解决电源毛刺和电源缓慢下降(电池电压不足)等问题引起的POR不可靠现象,有设计人员在RC电路中增加了二极管放电回路,在电源电压瞬间下降时使电容迅速放电,这样,一定宽度的电源毛刺也可令系统可靠复位。

2.3实例分析:快速开关机单片机启动不稳定

笔者曾经做过一个ZigBee物联网项目,采用ZigBe

RESET 硬件复位 嵌入式系统 上电复位 看门狗复位 相关文章:

- CPLD在DSP系统中的应用设计(04-11)

- Linux嵌入式系统开发平台选型探讨(11-09)

- 嵌入式系统中文输入法的设计(03-02)

- 基于MPC755的嵌入式计算机系统设计(05-10)

- WinCE下光电编码器的驱动程序设计(04-12)

- 为什么嵌入式开发人员要使用FPGA(05-13)