基于FPGA+DSP的高速中频采样信号处理平台的实现

alDSF++4.0,它是TigerSHARC系列DSP的集成开发环境,支持汇编语言、C语言、C++等开发语言,能让程序员使用这些工具编写出相对于特定DSP的高性能应用程序,发挥强大的处理能力。在本平台中,每片DSP的地位都是对等的,能够根据不同的要求,硬件结构不用改变,只须在DSP的软件算法中稍加改动,系统就能实现新的功能。

1.3 主控制电路设计

主控制电路与信号处理单元电路和外部接口电路相连,其核心是一片规模较小的FPGA。它主要是控制信号处理单元的同步复位及工作控制,可以将从外部主机接收到信号传递给信号处理单元,也可将信号处理单元的有关信息传递到外部主机中。

1.4 其他主要电路设计

时钟管理电路主要是负责板上FPGA、DSP、光口、高速A/D与D/A等正常工作所需要时钟生成与配置。外部存储电路是FPGA与DSP正常工作时所需要的外部RAM空间大小的设计。外部接口电路是本平台与其他设备进行连接的控制接口。光纤通道电路由两路光纤通道组成,每路可以工作在2.5 Gb/s,可以与其他系统进行数据交换。

2 性能测试

决定平台性能的指标有多个,选取最主要的三个进行测试,结果如下。

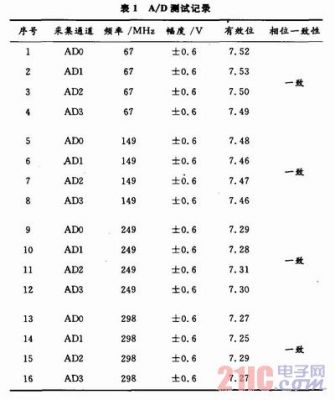

2.1 A/D采样的有效位数

有效位数是用来表述A/D器件的一项总体指标,对精确评价系统性能非常重要。对于A/D采样有效位的测试,采用A/D器件的最大量程输入,在FPGA中取得数据,用Matlab来对数据处理进行计算得到的。四路A/D采样通道有效位的测试数据如表1所示。

2.2 A/D通道间相位恒定

A/D通道间的相位恒定指标直接测试比较困难,在平台设计中已经保证了同一芯片两路A/D通道间的相位差是恒定的,只要测试两片A /D芯片输出时钟相位差是否恒定即可判定。表1中也显示了两片A/D器件输出时钟的相位差测试结果。

2.3 DSP运算速度

DSP的运算速度和精度决定着系统的数据处理能力,同时也会对整个系统的性能和结构产生重要的影响。DSP的处理能力可以用1 024点的复数FFT计算时间进行比较。Link口传递速度的测试,可以将Link口的工作时钟设定在600 MHz,按4 b进行数据传递,如果接收到数据没有错误,即可认定Link口的工作速率可以达到600 MB/s。经过测试,在工作频率为600 MHz,按4 b进行数据传递的情况下,各个Link均通过测试,也就是说每个Link口工作速率都可以达到600 MB/s。经过测试,平台上两个光口的传输速度均达到了2.5 Gb/s。DSP运算速度测试结果见表2。

3 结语

通过上述测试结果可以看出,本平台设计合理,FPGA与DSP的结合使用,能充分发挥各自的优势,实现对高速、多路、海量信号的实时处理。另外,高度集成化设计,大大减少了平台所占用的空间体积,也使功耗大大减小。平台在兵器某所项目验证中,接入实际雷达信号进行测试,各项指标均达到了设计要求。

- 用CPLD实现FIR数字滤波器的设计(08-07)

- 基于DSP的短波分集合成接收机(09-01)

- 数字信号处理器TMS320F241在变频空调中的应用(04-28)

- 什么是DSP及DSP技术详解(05-15)

- 数字信号处理(DSP)应用系统中的低功耗设计(05-02)

- 利用可编程逻辑实现灵活高效的多媒体信号处理(09-14)