基于DSP TMS320F2812的智能接口板设计

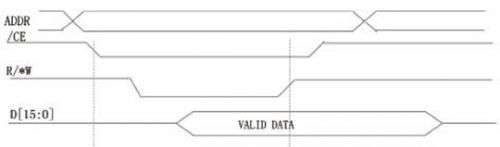

器写操作访问

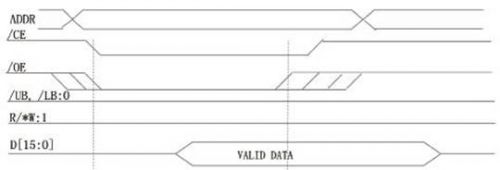

双口存储器的写操作时序如图4所示,/CE为写数据操作的片选信号,低电平有效;/UB、/LB是高/低字节有效控制信号,低电平有效,设计中将这两信号下拉;R/*W为输入控制信号,由系统写信号控制,低电平有效。

双口存储器BUSY信号使用及时序

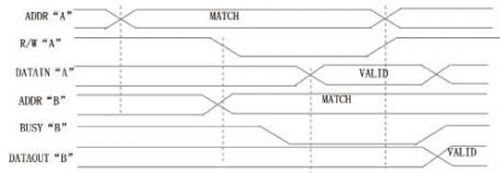

A/B通道对双口存储器的某一个单元同时进行访问时会出现竞争冒险,要避免这种情况的出现必须对访问信号判断优先级,IDT7025双口存储器通过自身硬件的BUSY信号引脚告知该CPU以使之根据需要对该单元重新访问或撤消访问,其操作时序如图5所示,BUSY信号低电平有效,R/W为读写信号。

图3 读操作及时序

图4 写操作及时序

图5 读写操作时序

时钟和复位电路

时钟电路

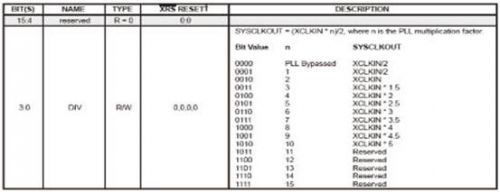

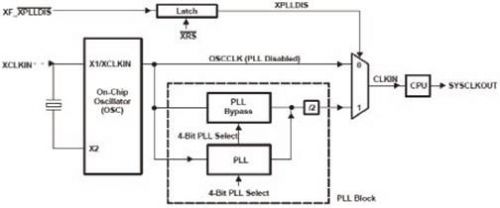

F2812处理器上有基于PLL的时钟模块,为器件及各种外设提供时钟信号。锁相环有4位倍频设置位,可以为处理器提供各种频率的时钟。时钟模块提供两种操作模式,如图6所示。

内部振荡器:如果使用内部振荡器,则必须在X1/XCLKIN和X2引脚之间连接一个石英晶体;

外部时钟:如果使用外部时钟,可以把时钟信号直接接到X1/XCLKIN引脚上,X2悬空。

外部XPLLDIS引脚用来选择系统时钟源。当XPLLDIS为低电平时,系统直接采用外部时钟作为系统时钟;当XPLLDIS为高电平时,外部时钟经过PLL倍频后,为系统提供时钟。系统通过锁相环控制寄存器来选择锁相环的工作模式和倍频系数,如表2所示。

表2 锁相环控制寄存器位定义

该接口板采用30M石英晶体提供时钟,XPLLDIS引脚上拉使能PLL模块,倍频选择最大的XCLKIN×5=150MHz。

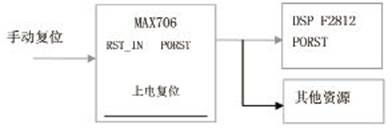

复位电路

复位电路会中断F2812的执行,复位板上资源,同时使处理器从0x3FF000地址开始执行指令序列。F2812的复位可由外部复位管脚引起。

F2812外部复位源采用MAX706芯片进行复位,MAX706复位的产生条件有以下3种情况:

a. 上电复位,当Vcc>4.40V(典型值)时产生复位,并保持200ms复位有效;

b. 掉电复位,当Vcc<4.40V(典型值)时产生复位,此时可防止对存储器进行错误写入;

c. 手动复位,当手动复位信号有效,产生复位,用于调试。

MAX706的复位信号形成F2812的上电复位输入,使系统所有资源复位。复位电路如图7所示。

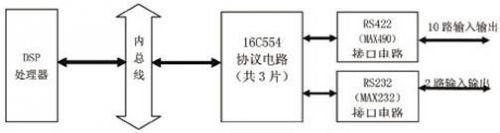

串行总线处理电路

本模块串行数据的接收和发送都采用TL16C554协议芯片来完成,RS422和RS232总线传输通过不同的接口芯片完成电平转换,其功能框图如图8所示。

图6 DSP时钟输入电路

图7 复位电路

图8 串行数据功能实现电路

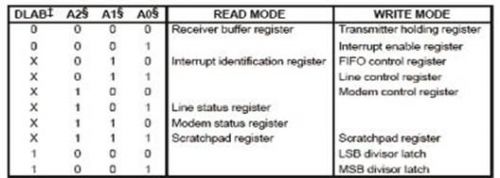

16C554通过对各个寄存器的编程完成串行数据的初始化及传输,在上电初始化时,本模块将串行数据初始化为数据位8位,停止位1位,无奇偶校验位,波特率为115.2KBPS,在完成上电BIT后,主机可通过改变双口存储器的初始化参数来满足自身对串行数据格式的约定,16C554各寄存器地址分配如表3,各个寄存器对应的访问地址为该串行通道分配的基地址加上偏移地址,即:各寄存器访问地址=BASE+[A2A1A0]16。

表3 协议芯片寄存器地址分配

串行协议芯片通过有效的初始化才能实现串行数据的正确接收和发送,在进行初始化的时候确保串行通道没有接收和发送数据。其初始化流程如表4所示。

表4 串行协议芯片初始化

控制逻辑电路

控制逻辑电路负责整个DSP数据处理模块上控制和状态信号的产生,负责PCI总线时序控制和逻辑译码。该逻辑功能由CPLD可编程逻辑器件实现,逻辑描述由VHDL语言完成。控制逻辑电路主要完成以下功能:

a. TMS320F2812总线时序支持电路;

b.系统总线接口时序支持电路;

c.地址译码;

d.地址转换及地址三态控制;

e.实现对数据总线管理逻辑的控制;

f.系统总线复位。

结束语

根据以上原理,我们研制了该智能接口板,通用性强,接口简单,可以满足大多数应用条件,经使用证明设计合理,稳定可靠。

TMS320F2812 智能接口板 DSP 相关文章:

- 基于DSP的无刷直流电机调速系统(06-01)

- TMS320F2812在多段液压机械无极变速器中的应用(11-10)

- 基于TMS320F2812的数字化三相变频电源的研制(01-15)

- 基于DSP的高精度数字频率计的设计(02-03)

- 基于TMS320F2812的分布式温度采集记录仪的设计与实现(11-29)

- 基于TMS320F2812的矢量变频调速系统研究(01-15)