最佳FPGA和专用DSP

时间:01-19

来源:电子产品世界 作者:益林

点击:

视频和静止图像的普遍采用,以及可配置系统(如软件无线电)日益增长的需求继续驱动DSP应用的扩展。很多应用需要经济有效的DSP处理。

虽然定制实现DSP功能,但在很多应用中几种功能,如FIR(有限脉冲响应)滤波器,IIR(无限脉冲响应)滤波器、FFT(快速傅里叶)和混频器是共同的。所有这些功能都需要与加、减、累加一起的乘法单元组合。

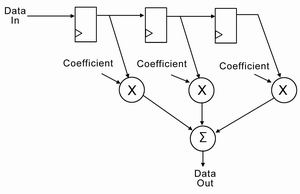

FIR滤波器(图1)存储n数据单元系列,每个数据单元延迟一个附加周期。通常,这些数据单元称之为分支。每个分支与系数相乘,其结果求和产生输出。某些方法并行执行所有的乘法。更一般的方法是分为N级,用累加器从一级到下一级传递结果。这些实现方法用功能资源换取速度,取N个计算级并需要n/N个乘法器。根据系数是静态还是动态以及系数值设计,有不少其他通用的设计最佳化方法。

实现方法

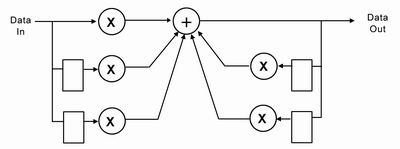

从图像压缩到确定数据取样的频谱成分,在不同的应用中都用FFT。实现FFT有多种方法。最通用的方法是通用Cooley-Tukey时间抽取,把FFT分解成若干更小的FFT。最简单的实现方法是用Radix-2蝶形单元(图2),其输入数据必须传递倍数。这种计算概念上是简单的;然而,图左边所有的乘和加是用复数计算的,所需要的乘和加的实数是更复杂的问题(如图右边所示)。

IIR滤滤器除引入反馈通路外,它类似于FIR滤波器。这些反馈通路使IIR滤波器的设计和分析比FIR更复杂。然而,对于相同硅面积,IIR方法可提供更强的滤波器。尽管有几种IIR结构,但是,一种通用的结构是用2阶四次方结构(图3)

很多应用是用混频器来变换信号频率。概念上,可用单个乘法器,而在数字应用中,用复数形式表示不少优点。最一般的形式是信号表示是为I和Q分量。

DSP选择

做为这些通用功能应用,大多数DSP应用的核心是乘、加、减或累加。通用DSP芯片与通用微处理器结合能有效地实现这些功能。乘法器数量通常1~4个,而微处理器通过乘和其他功能定序通过的数据,存储中间结果在存储器或累加器。主要靠提高乘法所用的时钟速度来提高性能。典型时钟速度为几十MHz~1GHz。性能用每秒MMAC(百万乘累加)度量,典型值10~4000。

需要较佳功能必须并联组合多个DSP引擎。这种方法的主要优点是直接实现用高级编程语言(如C语言)编写的算法。

DSP定向的FPGA能在一个芯片上并行实现很多功能。通用发送、逻辑和存储器资源互连功能、执行加法功能、定序和存储数据。某些基本器件仅提供乘法支持,需要用户建造其他逻辑功能。更复杂的器件提供加、减和累加功能做为DSP构建单元的一部分。FPGA通常带有几十乘法器单元,可工作在几百MHz的时钟频率。

DSP FPGA选择

Altera公司的Cyclone FPGA不包含DSP定向的元件,这使得实现大的DSP功能而不消耗大量的外部资源变得困难。然而,CycloneII包含乘法器功能,Xilinx公司的SpartanIII FPA家族具有基本的乘法器功能。没有DSP功能时,必须消耗大量的FPGA资源来实现一般设计中的加、减、累加和流水线寄存器。

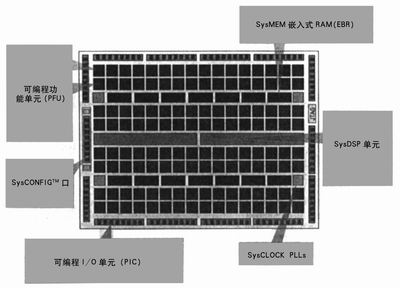

Lattice公司专为DSP应用设计了ECP-DSP器件(图4)。它含有与4和10个集成sysDSP单元连接的低成本FPEA结构。sysDSP单元以3个数据通路宽度(9,18和36)支持4个功能单元。用户为DSP单元选择一个功能单元,然后选择其操作数的宽度和类型(符号/无符号)。sysDSP单元中的操作数可以带符号或无符号,但在功能单元中不能混合。

同样,在一个单元中操作数宽度不能混合。每个sysDSPK中的资源可配置来支持MULT(乘)、MAC(乘累加)、MULTADD(乘加/减)和MULTADDSUM(乘加/减和)元件。

每个单元中可用的元件数取决于所选择的数据通路宽度。把若干个元件连接起来可并联实现DSP功能。

sysDSP单元在输入,中间和输出级具有内置任选流水线寄存器。如需要,输入也可能并行输入或跨过阵列移位。也为带符号和不带符号运算和加减之间动态转换提供选择。在sysDSP单元中可得到流水线寄存器、和、减和累加。在一般的功能中,一般需要用加、和或累加组合乘法。概念简单的流水线寄存器在宽数据通路中实现要消耗大量的资源。用sysDSP单元实现这些功能可使通用FPGA资源消耗较低、性能较高,允许采用较低速度等级的更小器件。

虽然定制实现DSP功能,但在很多应用中几种功能,如FIR(有限脉冲响应)滤波器,IIR(无限脉冲响应)滤波器、FFT(快速傅里叶)和混频器是共同的。所有这些功能都需要与加、减、累加一起的乘法单元组合。

FIR滤波器(图1)存储n数据单元系列,每个数据单元延迟一个附加周期。通常,这些数据单元称之为分支。每个分支与系数相乘,其结果求和产生输出。某些方法并行执行所有的乘法。更一般的方法是分为N级,用累加器从一级到下一级传递结果。这些实现方法用功能资源换取速度,取N个计算级并需要n/N个乘法器。根据系数是静态还是动态以及系数值设计,有不少其他通用的设计最佳化方法。

实现方法

从图像压缩到确定数据取样的频谱成分,在不同的应用中都用FFT。实现FFT有多种方法。最通用的方法是通用Cooley-Tukey时间抽取,把FFT分解成若干更小的FFT。最简单的实现方法是用Radix-2蝶形单元(图2),其输入数据必须传递倍数。这种计算概念上是简单的;然而,图左边所有的乘和加是用复数计算的,所需要的乘和加的实数是更复杂的问题(如图右边所示)。

IIR滤滤器除引入反馈通路外,它类似于FIR滤波器。这些反馈通路使IIR滤波器的设计和分析比FIR更复杂。然而,对于相同硅面积,IIR方法可提供更强的滤波器。尽管有几种IIR结构,但是,一种通用的结构是用2阶四次方结构(图3)

很多应用是用混频器来变换信号频率。概念上,可用单个乘法器,而在数字应用中,用复数形式表示不少优点。最一般的形式是信号表示是为I和Q分量。

DSP选择

做为这些通用功能应用,大多数DSP应用的核心是乘、加、减或累加。通用DSP芯片与通用微处理器结合能有效地实现这些功能。乘法器数量通常1~4个,而微处理器通过乘和其他功能定序通过的数据,存储中间结果在存储器或累加器。主要靠提高乘法所用的时钟速度来提高性能。典型时钟速度为几十MHz~1GHz。性能用每秒MMAC(百万乘累加)度量,典型值10~4000。

需要较佳功能必须并联组合多个DSP引擎。这种方法的主要优点是直接实现用高级编程语言(如C语言)编写的算法。

DSP定向的FPGA能在一个芯片上并行实现很多功能。通用发送、逻辑和存储器资源互连功能、执行加法功能、定序和存储数据。某些基本器件仅提供乘法支持,需要用户建造其他逻辑功能。更复杂的器件提供加、减和累加功能做为DSP构建单元的一部分。FPGA通常带有几十乘法器单元,可工作在几百MHz的时钟频率。

DSP FPGA选择

Altera公司的Cyclone FPGA不包含DSP定向的元件,这使得实现大的DSP功能而不消耗大量的外部资源变得困难。然而,CycloneII包含乘法器功能,Xilinx公司的SpartanIII FPA家族具有基本的乘法器功能。没有DSP功能时,必须消耗大量的FPGA资源来实现一般设计中的加、减、累加和流水线寄存器。

Lattice公司专为DSP应用设计了ECP-DSP器件(图4)。它含有与4和10个集成sysDSP单元连接的低成本FPEA结构。sysDSP单元以3个数据通路宽度(9,18和36)支持4个功能单元。用户为DSP单元选择一个功能单元,然后选择其操作数的宽度和类型(符号/无符号)。sysDSP单元中的操作数可以带符号或无符号,但在功能单元中不能混合。

同样,在一个单元中操作数宽度不能混合。每个sysDSPK中的资源可配置来支持MULT(乘)、MAC(乘累加)、MULTADD(乘加/减)和MULTADDSUM(乘加/减和)元件。

每个单元中可用的元件数取决于所选择的数据通路宽度。把若干个元件连接起来可并联实现DSP功能。

sysDSP单元在输入,中间和输出级具有内置任选流水线寄存器。如需要,输入也可能并行输入或跨过阵列移位。也为带符号和不带符号运算和加减之间动态转换提供选择。在sysDSP单元中可得到流水线寄存器、和、减和累加。在一般的功能中,一般需要用加、和或累加组合乘法。概念简单的流水线寄存器在宽数据通路中实现要消耗大量的资源。用sysDSP单元实现这些功能可使通用FPGA资源消耗较低、性能较高,允许采用较低速度等级的更小器件。

- 在采用FPGA设计DSP系统中仿真的重要性 (06-21)

- 基于 DSP Builder的FIR滤波器的设计与实现(06-21)

- 基于FPGA的快速并行FFT及其在空间太阳望远镜图像锁定系统中的应用(06-21)

- 3DES算法的FPGA高速实现(06-21)

- 用FPGA实现FFT算法(06-21)

- FPGA的DSP性能揭秘(06-16)