基于PCI总线和DSP芯片的图像处理平台的硬件设计

时间:07-06

来源:电子技术应用 作者:孔祥刚, 诸静

点击:

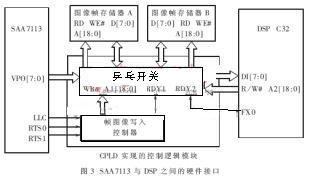

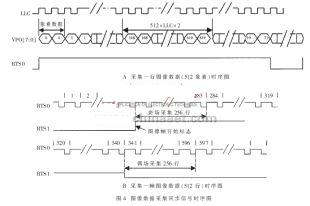

利用SAA7113的同步信号,帧图像写入控制器模块产生帧存储器的地址信号、写信号以及帧切换信号之一(RDY1)。SAA7113输出的同步信号包括LLC、RTS0、RTS1。LLC是行锁定系统时钟输出,为象素时钟频率的两倍,即27MHz,用来同步数据采集,使得一个LLC周期输出一个字节的图像数据。在图像数据有效时,其上升沿反相后作为帧存储器的WE#信号。RTS0、RTS1的功能是通过编程设置SAA7113功能寄存器确定的。RTS0被设置为水平输出参考信号(行有效信号),RTS0高电平时表示采集一行有效象素,低电平时表示场消隐信号,在RTSO上升沿后,帧图像写入控制器控制采集一行中间的512个象素数据,将其余的象素数据丢弃。RTS1被设置为垂直输出参考信号和奇偶场信号,RTS1高电平时表示采集奇场图像所需要的有效数据,在RTS1上升沿时,开始采集奇场图像数据,同时它也被用来作为帧图像开始的信号;RTS1低电平时表示采集偶场中所需要的图像数据,在RTS1下降沿时,开始采集偶场图像数据。在RTS1上升沿时,帧图像写入控制器控制采集256行象素数据作为奇场图像;在RTS1下降沿时,顺次采集下面的256行象素数据作为偶场图像,其余的图像行数据丢弃。使用512K×8bit的静态存储器(SRAM),恰好可以存放一帧512×512×2×8bit的图像。在合成一帧图像时,对应的奇场图像的第n个象素和偶场图像的第n个象素在存储器内位置相差512×2×8bit,帧图像写入控制器通过把RTS1(奇偶场有效)信号作为写入图像数据的帧存储器地址信号中的A1[11],把场中有效行的计数输出信号作为帧存储器地址信号中的A1[18:12],把行中有效象素的计数输出信号作为帧存储器地址信号中的A1[10:0],从而实现隔行信号变逐行信号存储在一图像帧存储器中。图4为图像采集同步信号时序图。当采集完一帧图像数据时,帧图像写入控制器产生RDY1信号,通知乒乓开关。

在DSP和SAA7113之间所有控制信号的接口逻辑和时序转换都由CPLD来完成,增加了可靠性,简化了PCB的版面,并且可以编程修改,提高了使用的灵活性。

4 S5933与DSP之间的接口设计

S5933的三种数据传输方式有不同的特点,应用于不同的场合。

S5933信箱方式不支持猝发(Burst)传输,由8个32位信箱寄存器组成,可从两个方向进行访问。它们平均分为两类,分别用于PCI接口和ADD-ON接口之间的双向信息传输。主机和扩展逻辑都可以通过查询或中断方式获悉任一信箱寄存器的任一字节的空满状态,并通过相应地址访问该字节。S5933的信箱寄存器映射在DSP的I/O空间中,从而可以实现DSP对信箱的直接操作,数据速率较低,故系统中只使用这种方式传输命令和状态信息,例如PC机通知DSP设备关闭;DSP通知上层已经传送完数据(处理完的数据的大小不是固定的)等。

S5933的FIFO方式主要由两个接口共用的两个32×8比特的FIFO、读或写地址寄存器以及读或写计数器组成。两个FIFO分别作为PCI和ADD-ON接口之间的双向缓冲区。S5933提供了快捷方式:一组专门用于FIFO方式传输的控制及状态信号,包括FIFO寄存器的直接读、写以及状态信号等,用以提高数据传输速度,但此信号组只能工作在S5933为主控设备的情况下。S5933作为目标设备时,内部FIFO只是作为一般的寄存器,PCI总线如同访问信箱寄存器那样访问它们,操作比较直观,但不支持猝发传输,极大地限制了传输速度;S5933作为主控设备时,FIFO方式可进行DMA方式的猝发传输,S5933可以通过FIFO接口启动DMA传输周期,传输过程不需要CPU的干预,传输的速率与外部设备的数据传输速率有关,可以得到很高的数据传输速率。S5933的DMA数据传输启动方式有两种:PCI总线接口启动和ADD-ON总线接口启动。启动方式决定于由哪个接口设置读或写地址寄存器以及读或写计数器:PCI总线接口启动方式是由PCI总线主设备(一般是PC机的客户程序)设置DMA相关寄存器发起DMA传输的;ADD-ON总线接口启动方式是由外部逻辑电路(一般是外部插卡上的CPU)设置DMA相关寄存器发起DMA传输的。

S5933的PASS-THRU方式使主机以内存映射方式访问ADD-ON接口的存储空间,只能工作在S5933是目标设备的情况下,且外部接口需要逻辑电路的支持,故不常用。

本系统是图像处理的一个实验平台,既要求数据传输率高,又要求有一定的升级功能和灵活性。因此,系统采用FIFO数据传输方式。当采集的图像数据量大且要求传输速度高时,可以采用FIFO方式中的PCI总线接口启动DMA方式,使用DMA传输;有一些应用场合,要传送的数据个数不明确,例如图像压缩后的数据量是不一定的,可以使用外加总线接口启动DMA的传输方式传送压缩图像,而用信箱方式传送命令和图像状态信息。在这种方式下,S5933的外加总线操作寄存器全部映射在TMS320C32 DSP的选通控制信号IOSTRB#控制的空间中,使DSP对PCI接口传输的数据的控制十分简单,就象操作自身的外围接口一样。S5933与DSP之间的硬件接口的具体连接方式如图5所示。

DSP PCI总线 图像处理 TMS320C32 相关文章:

- 在采用FPGA设计DSP系统中仿真的重要性 (06-21)

- 基于 DSP Builder的FIR滤波器的设计与实现(06-21)

- 达芬奇数字媒体片上系统的架构和Linux启动过程(06-02)

- FPGA的DSP性能揭秘(06-16)

- 用CPLD实现DSP与PLX9054之间的连接(07-23)

- DSP+FPGA结构在雷达模拟系统中的应用(01-02)