基于DSP的图象采集与处理系统的设计

时间:06-15

来源:电子元器件应用 作者:栾璟明,雷志勇

点击:

3.2 图像输出接口设计

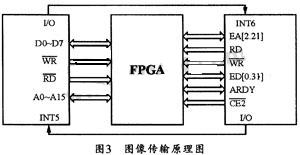

TMS320C6711与AN2131QC采用并口方式进行通讯。DSP为32位处理器,其并行接口数据线为32根,而AN213 I QC的并行口为8位,若将DSP32根数据线中的8根数据线直接与USB并口相连,则DSP传送一个32位数据需进行4次操作,这显然会影响系统的效率。因此,可采用8位/32位数据线转换和数据缓冲设备来将两者相连。考虑到性能价格等因素,本设计采用FPGA作为两者之间的缓冲设备,实现从DSP到USB数据传输缓冲以及32位数据线转8位数据线功能。FPGA采用X ilinx公司SpartanIIE系列的XC2SSOE芯片作为转换器。其图像传输电路原理图如图3所示。

4.1 DSP的软件开发

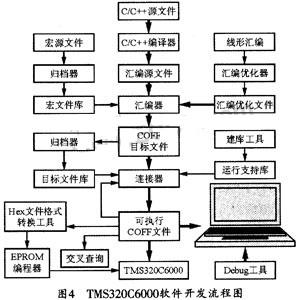

TMS320C6000软件开发的一切过程都可在CCS集成环境下进行,包括项目的建立、源代码的编辑以及程序的编译和调试。图4所示是TMS320C6000的软件开发流程图。其中黑体部分是开发C代码的常规流程,其它功能可用于辅助和加速软件开发过程。

汇编优化器是C6000代码产生工具内极具特色的一部分。它在DSP业界首创了对线性汇编代码自动进行优化的技术。线性汇编语言是为简化C6000汇编语言程序的开发而设计的,它不是独立的编程语言。它可用用户编写的线性汇编代码作为输入,同时产生一个标准汇编代码作为输出。与C6000的标准汇编语言相比,采用线性汇编不需要考虑并行指令安排、指令延迟和寄存器,而由汇编优化器自动完成,其所产生的代码效率可以达到人工编写代码效率的95%-100%,同时还可以降低编程工作量,缩短开发周期。

C6000程序的调试和仿真有两种模式:软件仿真和硬件仿真。软件仿真时,其程序的执行完全靠主机上的仿真软件模拟,程序单步或者运行的结果都是仿真软件"计算"出来的。而硬件仿真需要目标板。仿真程序利用开发系统将代码下载到DSP,程序是在芯片上直接运行的。仿真软件只是把运行结果读出来显示。软件仿真无需目标板就可以开始软件编程,但仿真速度较慢,而且无法仿真某些外设的功能。硬件仿真的优点是仿真速度快,仿真结果与实际结果一致。

4.2 系统的上电引导

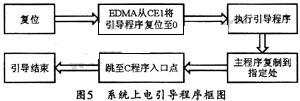

C6711的引导装载方式有三种:一是无引导,二是ROM/FLASH引导,三是主机引导。本设计采用FLASH引导。根据DSK开发板上EMIF与FIASH硬件电路连接设计的引导程序如图5所示。

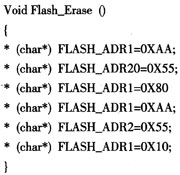

擦除FLASH存储器的关键源代码如下:

#define FLASH_ADR1 0X90000555

#define FLASH_ADR2 0X900002AA

(2)汇编源代码文件

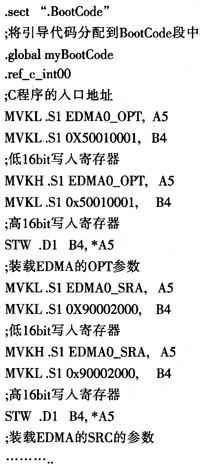

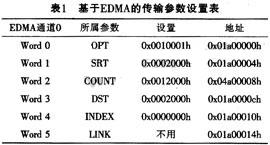

本引导代码的主要功能是将用户程序段从FLASH复制到DSP内部RAM中。然后再跳转到程序的入口处开始执行主程序。这里采用的是EDMA快速实现DSP存储空间数据搬移的方式。基于EDMA传输参数的设置方法如表1所列。其核心引导程序如下:

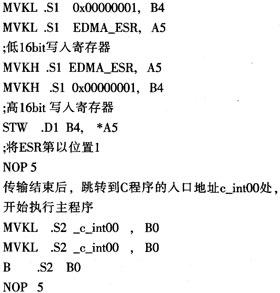

启动EDMA复制主程序段:CPU可以通过写事件置位寄存器(ESR)启动一个EDMA通道,ESR中某一位写1时,将强行触发对应的事件。程序如下:

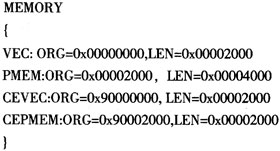

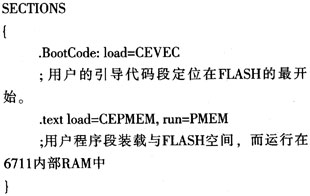

系统中的链接命令文件(boot.cmd)如下:

引导装载是设计DSP系统所必需的过程。本设计采用EDMA方式来实现程序的快速搬移,故可在自制的PCB板上正确地实现脱机运行。

(4)对DSP寄存器的设置

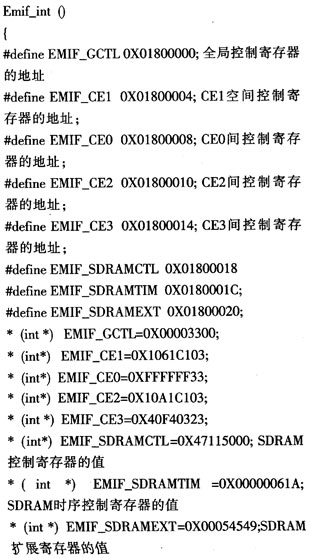

只有对相应的寄存器实现EMIF初始化,DSP才能访问外部存储器的数据,其源代码如下:

本文介绍了为了在线线圈直径的测量而开发线阵CCD图像采集和处理设备的具体方法,该系统利用TI公司的高性能浮点DSP-TMS320C6711实现了对dalsa公司的Piranha2 P2-2x Camera输出数据的采集与处理。给出了一种通用的实时图像处理系统,并详细讨论了系统的具体结构。在该系统中运行一些基本的图像处理(锐化,平滑,边缘检测)和压缩算法(JPEG,H.263),都能达到实时处理的目的。但在实际应用中,由于要求进行连续采集与处理,最好能采用多个DSP并行工作方式。若物体的运动速度更快或图像处理更复杂时,还应采用性能更强的DSP(如TI的64X系列DSP或采用多个DSP并行处理)。另外,在DSP与USB通讯设计中引人FPGA可使系统的设计更加灵活,同时也可为系统以后的扩展提供方便。

TMS320C6711与AN2131QC采用并口方式进行通讯。DSP为32位处理器,其并行接口数据线为32根,而AN213 I QC的并行口为8位,若将DSP32根数据线中的8根数据线直接与USB并口相连,则DSP传送一个32位数据需进行4次操作,这显然会影响系统的效率。因此,可采用8位/32位数据线转换和数据缓冲设备来将两者相连。考虑到性能价格等因素,本设计采用FPGA作为两者之间的缓冲设备,实现从DSP到USB数据传输缓冲以及32位数据线转8位数据线功能。FPGA采用X ilinx公司SpartanIIE系列的XC2SSOE芯片作为转换器。其图像传输电路原理图如图3所示。

4.1 DSP的软件开发

TMS320C6000软件开发的一切过程都可在CCS集成环境下进行,包括项目的建立、源代码的编辑以及程序的编译和调试。图4所示是TMS320C6000的软件开发流程图。其中黑体部分是开发C代码的常规流程,其它功能可用于辅助和加速软件开发过程。

汇编优化器是C6000代码产生工具内极具特色的一部分。它在DSP业界首创了对线性汇编代码自动进行优化的技术。线性汇编语言是为简化C6000汇编语言程序的开发而设计的,它不是独立的编程语言。它可用用户编写的线性汇编代码作为输入,同时产生一个标准汇编代码作为输出。与C6000的标准汇编语言相比,采用线性汇编不需要考虑并行指令安排、指令延迟和寄存器,而由汇编优化器自动完成,其所产生的代码效率可以达到人工编写代码效率的95%-100%,同时还可以降低编程工作量,缩短开发周期。

C6000程序的调试和仿真有两种模式:软件仿真和硬件仿真。软件仿真时,其程序的执行完全靠主机上的仿真软件模拟,程序单步或者运行的结果都是仿真软件"计算"出来的。而硬件仿真需要目标板。仿真程序利用开发系统将代码下载到DSP,程序是在芯片上直接运行的。仿真软件只是把运行结果读出来显示。软件仿真无需目标板就可以开始软件编程,但仿真速度较慢,而且无法仿真某些外设的功能。硬件仿真的优点是仿真速度快,仿真结果与实际结果一致。

4.2 系统的上电引导

C6711的引导装载方式有三种:一是无引导,二是ROM/FLASH引导,三是主机引导。本设计采用FLASH引导。根据DSK开发板上EMIF与FIASH硬件电路连接设计的引导程序如图5所示。

擦除FLASH存储器的关键源代码如下:

#define FLASH_ADR1 0X90000555

#define FLASH_ADR2 0X900002AA

(2)汇编源代码文件

本引导代码的主要功能是将用户程序段从FLASH复制到DSP内部RAM中。然后再跳转到程序的入口处开始执行主程序。这里采用的是EDMA快速实现DSP存储空间数据搬移的方式。基于EDMA传输参数的设置方法如表1所列。其核心引导程序如下:

启动EDMA复制主程序段:CPU可以通过写事件置位寄存器(ESR)启动一个EDMA通道,ESR中某一位写1时,将强行触发对应的事件。程序如下:

系统中的链接命令文件(boot.cmd)如下:

引导装载是设计DSP系统所必需的过程。本设计采用EDMA方式来实现程序的快速搬移,故可在自制的PCB板上正确地实现脱机运行。

(4)对DSP寄存器的设置

只有对相应的寄存器实现EMIF初始化,DSP才能访问外部存储器的数据,其源代码如下:

本文介绍了为了在线线圈直径的测量而开发线阵CCD图像采集和处理设备的具体方法,该系统利用TI公司的高性能浮点DSP-TMS320C6711实现了对dalsa公司的Piranha2 P2-2x Camera输出数据的采集与处理。给出了一种通用的实时图像处理系统,并详细讨论了系统的具体结构。在该系统中运行一些基本的图像处理(锐化,平滑,边缘检测)和压缩算法(JPEG,H.263),都能达到实时处理的目的。但在实际应用中,由于要求进行连续采集与处理,最好能采用多个DSP并行工作方式。若物体的运动速度更快或图像处理更复杂时,还应采用性能更强的DSP(如TI的64X系列DSP或采用多个DSP并行处理)。另外,在DSP与USB通讯设计中引人FPGA可使系统的设计更加灵活,同时也可为系统以后的扩展提供方便。

USB DSP 图象采集与处理 FPGA Camera Link 相关文章:

- Linux系统下USB摄像头驱动程序开发(04-25)

- 基于uClinux嵌入式系统的汽车黑匣子的设计(07-08)

- 基于WinCE操作系统的通用USB数控键盘设计(08-05)

- 基于WinCE的ARM视频监控系统(11-14)

- 基于LabVIEW的USB实时数据采集处理系统的实现(03-26)

- 基于DSP和USB的高速数据采集与处理系统设计(05-01)