FPGA为传统DSP应用提供灵活的可重配置解决方案

时间:08-17

来源:电子工程专辑

点击:

信号处理是连接现实世界和数字运算世界的桥梁。随着用数字信号处理实现的算法变得日益复杂,对这些算法的性能要求呈指数上升。针对成本敏感的大批量设备,比如蜂窝电话、机顶盒和电脑图形卡等,这一要求正在大力推动非常特殊的特殊应用标准产品(ASSP)的开发。然而对许多其它设备来说,实现高性能数字信号处理的唯一选择是通用数字信号处理器(DSP)以及最新的现场可编程门阵列(FPGA)。

这些设备中有许多是采用DSP实现的。虽然DSP可以通过软件进行编程,但DSP硬件架构很不灵活。DSP的性能受很多固定硬件架构的限制,如总线性能瓶颈、固定数量的乘法累加(MAC)模块、固定存储器、固定硬件加速模块和固定数据带宽等。因此DSP的这种固定硬件架构对于许多要求定制DSP功能实现的应用来说并不适用。

FPGA可以为实现传统DSP应用提供可重配置解决方案,并能比DSP提供更高的吞吐量和原始数据处理能力。由于FPGA的硬件是可配置的,因此它能在提供完整的硬件定制功能的同时实现各种DSP应用。用FPGA实现的DSP系统可以具有定制的架构、定制的总线结构、定制的存储器、定制的硬件加速模块和可变数量的MAC模块。

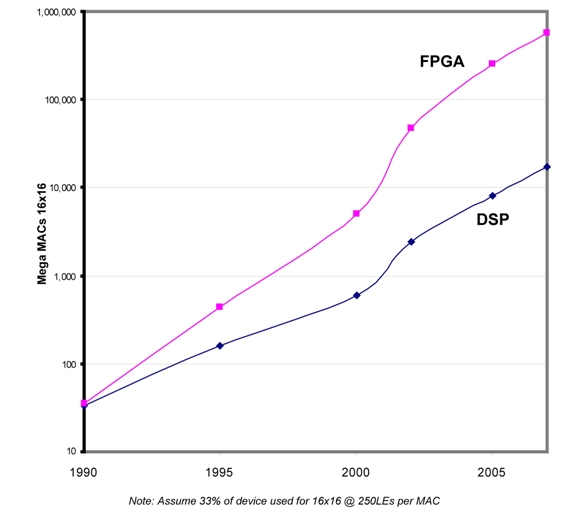

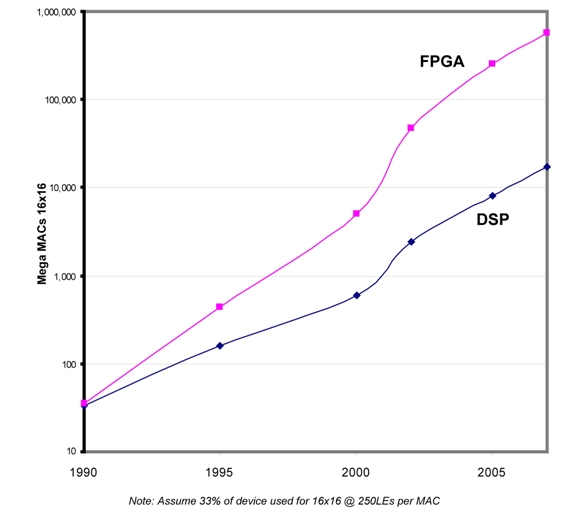

自从新千年伊始,FPGA就已经拥有了专用数字信号处理(DSP)功能。过去六年来,FPGA提供的DSP性能已经提高了16倍之多,达到每秒500千兆次乘法-累加操作(GMACS)。在相同时期内,数字信号处理器的性能只从1.6GMACS提高到了目前的8GMACS。许多设备只需要少量的DSP性能,相当于类似Altera公司Cyclone II的FPGA提供的性能。不过,对于要求许多数字信号处理器的高性能设备来说,单个Altera Stratix III FPGA也能替代这些处理器,从而不仅能够提供超过等效的DSP性能,还能显著地减少系统功耗、以及电路板面积和成本。

对高性能DSP需求的关键驱动力来自无线通信基础设施、视频广播设备、医疗成像和军事应用。FPGA已经成为能够满足这些要求的首选可编程DSP平台。

第三代通信基站平台是需要使用大量DSP的系统之一,它包括了一块射频卡和一块通道卡以及两个主处理区。第三代无线通信产品大部分是宽带产品,因此其射频元件通常工作在线性范围之外。先进的算法有助于满足远高于传统数字信号处理器能力的处理要求。无线基础设施中的主要设备现主要依靠FPGA实现射频线性化处理。

图1:近年来FPGA与DSP性能的演变情况。

FPGA成为首选处理平台的另外一个领域是WiMAX基带处理设备,它所采用的正交频分复用(OFDM)技术的巨大运算要求只能用特殊应用集成电路(ASIC)或FPGA才能满足。由于ASIC太贵,开发风险很大,因此FPGA成为了WiMAX市场的赢家。

使FPGA成为DSP领域理想解决方案的关键性能是什么?大量的乘法器、高的片上存储器带宽、大量I/O带宽以及由于可编程逻辑带来的独特且完全灵活的FPGA架构都确保了没有其它可编程技术可以提供相同的DSP性能。与其它半导体解决方案相比,FPGA可以在更低的功耗下提供最高性能的可编程DSP功能,同时还能降低系统成本和减小电路板面积。

系统设计师可以用一片或几片FPGA开发出一块原本要数十块DSP和可能多块电路板才能实现的电路板。因为FPGA支持在相同封装内的纵向移植,因此可以在无需多电路板设计的条件下很容易将单板和系统设计从低端功能升级到最高功能。这种灵活性是很大的优势,因为它能减小产品线工程设计和验证成本。

图2. 第三代通信基站处理架构方框图。

FPGA DSP有哪些新功能呢?随着Stratix III FPGA系列器件的推出,DSP功能也有了新的发展,比如密度翻倍、性能显著提升、功耗显著降低,I/O性能也得到了增强,DSP模块有了重大创新。

增加DSP模块中的片上乘法器数量(最多是896个18×18乘法器)是重大的创举。它允许在更少的硅片面积中封装更多的乘法器,同时能降低功耗。DSP模块通常是针对性能、灵活性和低功率做过优化的硬模块。DSP硅模块有两种物理约束:外设数量和使用面积大小。

DSP模块的外围有144根输入线和144根输出线,还有一些控制信号。DSP模块的面积可以实现4个18×18的乘法器以及相应总的输入输出信号。对DSP模块如何发展的芯片级和系统级研究的依据是那些特殊应用需求以及向65nm工艺技术转移所产生的后果。

在芯片级,改变外设与DSP模块面积的比例可以形成更多的I/O或更多的模块级逻辑。在系统级,对DSP算法的调查表明乘法器逻辑的主要使用者是滤波和变换算法,它们都依赖于乘法累加操作来满足大部分处理要求。在需要时通过优化DSP模块的内核面积可以增加一倍的乘法累加操作次数,从而降低相对于总体运算的外围I/O要求。通过在一个DSP模块中完成更多的DSP算法,总的芯片效率就能有显著的提高。

带8个18×18乘法器和相关寄存器、累加器以及取舍电路的DSP模块如图3所示。乘法器的使用限制于DSP模块的输出线,而非逻辑面积。与竞争性架构相比,这种架构可以使硅片效率约提高50%。

图3:Stratix III DSP模块架构。

模块的总体DSP功能减少了使用乘法累加操作的标准算法,如有限脉冲响应(FIR)滤波器或复杂乘法器,同时由于不需要使用可编程逻辑矩阵而减少了总体功率和资源消耗。当乘法累加操作作为算法的一部分被包含时,可以极大地增加18×18乘法器的数量。

对许多系统架构来说,FPGA的一个突出优点是封装的纵向移植性。纵向移植可以使单块电路板设计无需重做就能支持灵活的处理性能和成本。系统架构师可以运用这一功能开发出具有各种价位和性能的产品,却不会显著影响开发成本或库存。另外,随着Altera’s HardCopy结构化ASIC的推出,当需要考虑大批量和高性价比结构时可以获得额外的性价比。

无线基础架构应用是如何运用这种灵活性的一个很好例子。在灵活的通道单元盘中使用的FPGA支持各种标准,通过纵向移植还能支持各种通道密度。一个基站可以被配置为最少的通道数,也可以使用相同的基础架构对通道进行大扩容,只需改变专门的FPGA选择。在许多发展中国家,注意力往往放在更灵活、可升级和业务丰富的设备上,这些设备就需要FPGA的这种灵活性。在这些对价格特别敏感的地区,同一产品中非常标准化的功能可以使用HardCopy结构化ASIC以更低的成本来实现。采用这种解决方案的供应商将拥有强大的技术优势,无需增加工程成本就能提高业务的灵活性。

FPGA的I/O带宽比DSP的带宽要大得多。I/O带宽是满足系统处理要求的关键要素,而带宽又受数据输入输出以及片外数据存储器的影响。在对存储器有很高要求的应用场合,Stratix III存储器接口支持400MHz的DDR3存储器,这个外部存储器带宽要比目前最先进的DSP高16倍。

因为系统级开发工具可以帮助系统架构师实现灵活性、可发展性、可维修性和高性能信号处理及控制架构,因此FPGA在过去几年中发展非常迅速。这些工具包括DSP系统建模工具、系统综合工具、控制处理IP、自动的C语言到硬件加速和DSP优化的应用IP。设计师利用这些工具可以快速建立真正得到优化以满足系统要求的高性能架构。在纵向移植和HardCopy结构化ASIC的支持下,系统架构师可以根据产品线要求实现可扩展性能,实现各种产品以满足不同市场要求,同时实现实质性的生产效益。

目前已经有完整开发FPGA中架构所必需的工具和IP,但系统架构中为何需要标准的第三方处理器还有其它原因。当第三方处理器与FPGA一起使用时,它能通过一种被称为FPGA协处理的架构技术显著地提高系统性能,同时降低系统成本、功耗和电路板面积。在FPGA协处理过程中,FPGA可以从第三方处理器卸载处理任务繁重的算法。许多系统使用控制处理器、数字信号处理器和一个或多个FPGA(在FPGA中执行主要的处理负载),其中控制和DSP用于满足传统软件、操作系统要求或针对最终应用(如Windows GUI控制)的处理适用性。

高性能系统的核心信号处理将越来越多地转向FPGA。FPGA可以提供其他任何半导体器件无法提供的最高的可编程DSP性能,在加上纵向移植以及面向低成本器件的HardCopy技术,目前没有那种比此更灵活的系统架构解决方案能更好地满足性能、低功耗、低成本和产品广度及寿命要求。

作者:Paul Ekas

高级产品经理

Altera公司

这些设备中有许多是采用DSP实现的。虽然DSP可以通过软件进行编程,但DSP硬件架构很不灵活。DSP的性能受很多固定硬件架构的限制,如总线性能瓶颈、固定数量的乘法累加(MAC)模块、固定存储器、固定硬件加速模块和固定数据带宽等。因此DSP的这种固定硬件架构对于许多要求定制DSP功能实现的应用来说并不适用。

FPGA可以为实现传统DSP应用提供可重配置解决方案,并能比DSP提供更高的吞吐量和原始数据处理能力。由于FPGA的硬件是可配置的,因此它能在提供完整的硬件定制功能的同时实现各种DSP应用。用FPGA实现的DSP系统可以具有定制的架构、定制的总线结构、定制的存储器、定制的硬件加速模块和可变数量的MAC模块。

自从新千年伊始,FPGA就已经拥有了专用数字信号处理(DSP)功能。过去六年来,FPGA提供的DSP性能已经提高了16倍之多,达到每秒500千兆次乘法-累加操作(GMACS)。在相同时期内,数字信号处理器的性能只从1.6GMACS提高到了目前的8GMACS。许多设备只需要少量的DSP性能,相当于类似Altera公司Cyclone II的FPGA提供的性能。不过,对于要求许多数字信号处理器的高性能设备来说,单个Altera Stratix III FPGA也能替代这些处理器,从而不仅能够提供超过等效的DSP性能,还能显著地减少系统功耗、以及电路板面积和成本。

对高性能DSP需求的关键驱动力来自无线通信基础设施、视频广播设备、医疗成像和军事应用。FPGA已经成为能够满足这些要求的首选可编程DSP平台。

第三代通信基站平台是需要使用大量DSP的系统之一,它包括了一块射频卡和一块通道卡以及两个主处理区。第三代无线通信产品大部分是宽带产品,因此其射频元件通常工作在线性范围之外。先进的算法有助于满足远高于传统数字信号处理器能力的处理要求。无线基础设施中的主要设备现主要依靠FPGA实现射频线性化处理。

图1:近年来FPGA与DSP性能的演变情况。

FPGA成为首选处理平台的另外一个领域是WiMAX基带处理设备,它所采用的正交频分复用(OFDM)技术的巨大运算要求只能用特殊应用集成电路(ASIC)或FPGA才能满足。由于ASIC太贵,开发风险很大,因此FPGA成为了WiMAX市场的赢家。

使FPGA成为DSP领域理想解决方案的关键性能是什么?大量的乘法器、高的片上存储器带宽、大量I/O带宽以及由于可编程逻辑带来的独特且完全灵活的FPGA架构都确保了没有其它可编程技术可以提供相同的DSP性能。与其它半导体解决方案相比,FPGA可以在更低的功耗下提供最高性能的可编程DSP功能,同时还能降低系统成本和减小电路板面积。

系统设计师可以用一片或几片FPGA开发出一块原本要数十块DSP和可能多块电路板才能实现的电路板。因为FPGA支持在相同封装内的纵向移植,因此可以在无需多电路板设计的条件下很容易将单板和系统设计从低端功能升级到最高功能。这种灵活性是很大的优势,因为它能减小产品线工程设计和验证成本。

图2. 第三代通信基站处理架构方框图。

FPGA DSP有哪些新功能呢?随着Stratix III FPGA系列器件的推出,DSP功能也有了新的发展,比如密度翻倍、性能显著提升、功耗显著降低,I/O性能也得到了增强,DSP模块有了重大创新。

增加DSP模块中的片上乘法器数量(最多是896个18×18乘法器)是重大的创举。它允许在更少的硅片面积中封装更多的乘法器,同时能降低功耗。DSP模块通常是针对性能、灵活性和低功率做过优化的硬模块。DSP硅模块有两种物理约束:外设数量和使用面积大小。

DSP模块的外围有144根输入线和144根输出线,还有一些控制信号。DSP模块的面积可以实现4个18×18的乘法器以及相应总的输入输出信号。对DSP模块如何发展的芯片级和系统级研究的依据是那些特殊应用需求以及向65nm工艺技术转移所产生的后果。

在芯片级,改变外设与DSP模块面积的比例可以形成更多的I/O或更多的模块级逻辑。在系统级,对DSP算法的调查表明乘法器逻辑的主要使用者是滤波和变换算法,它们都依赖于乘法累加操作来满足大部分处理要求。在需要时通过优化DSP模块的内核面积可以增加一倍的乘法累加操作次数,从而降低相对于总体运算的外围I/O要求。通过在一个DSP模块中完成更多的DSP算法,总的芯片效率就能有显著的提高。

带8个18×18乘法器和相关寄存器、累加器以及取舍电路的DSP模块如图3所示。乘法器的使用限制于DSP模块的输出线,而非逻辑面积。与竞争性架构相比,这种架构可以使硅片效率约提高50%。

图3:Stratix III DSP模块架构。

模块的总体DSP功能减少了使用乘法累加操作的标准算法,如有限脉冲响应(FIR)滤波器或复杂乘法器,同时由于不需要使用可编程逻辑矩阵而减少了总体功率和资源消耗。当乘法累加操作作为算法的一部分被包含时,可以极大地增加18×18乘法器的数量。

对许多系统架构来说,FPGA的一个突出优点是封装的纵向移植性。纵向移植可以使单块电路板设计无需重做就能支持灵活的处理性能和成本。系统架构师可以运用这一功能开发出具有各种价位和性能的产品,却不会显著影响开发成本或库存。另外,随着Altera’s HardCopy结构化ASIC的推出,当需要考虑大批量和高性价比结构时可以获得额外的性价比。

无线基础架构应用是如何运用这种灵活性的一个很好例子。在灵活的通道单元盘中使用的FPGA支持各种标准,通过纵向移植还能支持各种通道密度。一个基站可以被配置为最少的通道数,也可以使用相同的基础架构对通道进行大扩容,只需改变专门的FPGA选择。在许多发展中国家,注意力往往放在更灵活、可升级和业务丰富的设备上,这些设备就需要FPGA的这种灵活性。在这些对价格特别敏感的地区,同一产品中非常标准化的功能可以使用HardCopy结构化ASIC以更低的成本来实现。采用这种解决方案的供应商将拥有强大的技术优势,无需增加工程成本就能提高业务的灵活性。

FPGA的I/O带宽比DSP的带宽要大得多。I/O带宽是满足系统处理要求的关键要素,而带宽又受数据输入输出以及片外数据存储器的影响。在对存储器有很高要求的应用场合,Stratix III存储器接口支持400MHz的DDR3存储器,这个外部存储器带宽要比目前最先进的DSP高16倍。

因为系统级开发工具可以帮助系统架构师实现灵活性、可发展性、可维修性和高性能信号处理及控制架构,因此FPGA在过去几年中发展非常迅速。这些工具包括DSP系统建模工具、系统综合工具、控制处理IP、自动的C语言到硬件加速和DSP优化的应用IP。设计师利用这些工具可以快速建立真正得到优化以满足系统要求的高性能架构。在纵向移植和HardCopy结构化ASIC的支持下,系统架构师可以根据产品线要求实现可扩展性能,实现各种产品以满足不同市场要求,同时实现实质性的生产效益。

目前已经有完整开发FPGA中架构所必需的工具和IP,但系统架构中为何需要标准的第三方处理器还有其它原因。当第三方处理器与FPGA一起使用时,它能通过一种被称为FPGA协处理的架构技术显著地提高系统性能,同时降低系统成本、功耗和电路板面积。在FPGA协处理过程中,FPGA可以从第三方处理器卸载处理任务繁重的算法。许多系统使用控制处理器、数字信号处理器和一个或多个FPGA(在FPGA中执行主要的处理负载),其中控制和DSP用于满足传统软件、操作系统要求或针对最终应用(如Windows GUI控制)的处理适用性。

高性能系统的核心信号处理将越来越多地转向FPGA。FPGA可以提供其他任何半导体器件无法提供的最高的可编程DSP性能,在加上纵向移植以及面向低成本器件的HardCopy技术,目前没有那种比此更灵活的系统架构解决方案能更好地满足性能、低功耗、低成本和产品广度及寿命要求。

作者:Paul Ekas

高级产品经理

Altera公司

- 在采用FPGA设计DSP系统中仿真的重要性 (06-21)

- 基于 DSP Builder的FIR滤波器的设计与实现(06-21)

- 基于FPGA的快速并行FFT及其在空间太阳望远镜图像锁定系统中的应用(06-21)

- 3DES算法的FPGA高速实现(06-21)

- 用FPGA实现FFT算法(06-21)

- FPGA的DSP性能揭秘(06-16)