100GHz频率!软性电子怎么做到的?

美国威斯康辛大学-麦迪逊分校(UW-Madison)的研究人员利用软性矽奈米薄膜(NM)的载子迁移率高以及奈米压印微影(NIM)技术可扩充的优点,打造出能作业于38GHz频率的软性薄膜RF电晶体。

根据研究人员的模拟结果,新的制造策略能以低成本与低温在大型PET胶卷上实现100GHz性能的软性薄膜RF电晶体。

研究人员在最新一期的《科学报告》期刊中发表"具有奈米沟槽结构的快速软性电晶体"(Fast Flexible Transistors with a Nanotrench Structure)一文,详细介绍他们如何克服传统微影技术限制。

研究人员们并非选择性地掺杂矽基板以制作电晶体图案,而是毫无差别地掺杂整个矽奈米薄膜(由SOI晶圆制造而来),从而使矽块材保有较典型低迁移率有机材料更优越的电荷载子迁移率。

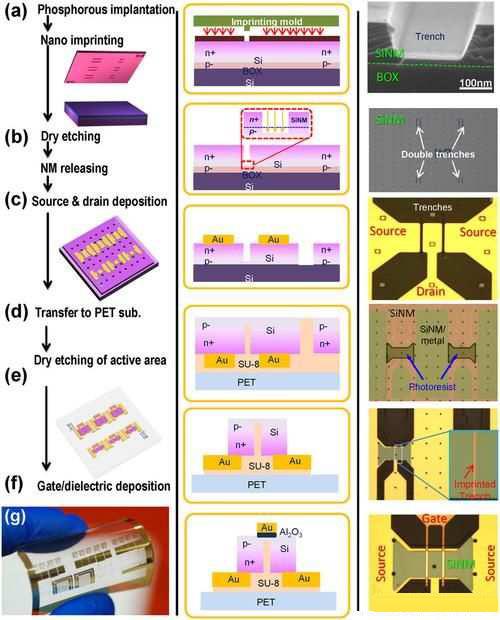

接着,研究人员用电子束微影法蚀刻奈米压印模具,使其得以透过光阻层压印蚀刻光罩图案,随后再用于Si NM(宽100nm x 深250nm)蚀刻深层奈米沟槽。在沈积源极与汲极电极以及削薄埋入氧化物以释放Si NM后,活性的奈米薄膜被翻转并转印至涂覆粘合剂的PET基板上。更深层的干式蚀刻定义出活性区域的边界,然后在100nm沟槽上沈积Al2O3闸电介质与金闸电极,以实现最终的电晶体。

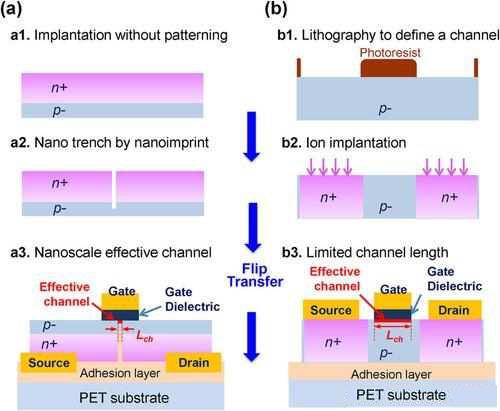

比较元件结构(横截面图)与(a) 3-D奈米沟槽Si NM软性RF TFT以及(b)传统2-D TFT之间的制造制程。有效通道长度Lch以红色标示(a3,b3),奈米沟槽TFT经由NIL可达到50nm的最小Lch,而传统TFT则只能达到1.5?μm。(a1)覆盖磷离子注入与热退火;(a2)透过奈米压印形成奈米沟槽;(a3) 奈米沟槽TFT的最终结构,通道长度Lch由奈米压印定义;(b1) 光微影为离子注入定义S/D区域;(b2) 选择性离子注入与热退火;(b3)传统TFT的最终结构,通道长度Lch受限于闸电极,并在离子注入与热退火期间掺杂向外扩散

值得注意的是,所有的元件制造过程都必须在低于150°C的温度下进行(除了第一次掺杂以及由SOI释放Si NM之前以覆盖方式重复结晶的步骤)。

图2:奈米沟槽Si NM RF TFT的原理图(左栏)、横截面(中间)以及相应的显微影像(右栏)。(a)以NIL在磷注入的 p? SOI基板定义奈米沟槽; (b)干式蚀刻分离n+区域,以便从源极至汲极形成n+/p?/n+路径;(c)在削薄埋入氧化层以释放Si NM(形成活性区域以及源极与汲极触点)后部份完成的TFT;(d)翻转具源极与汲极电极的Si NM至涂覆粘合剂的PET基板上;(e)干式蚀刻活性区域周围;(f)沈积沟槽上方的Al2O3闸电极层与金闸电极;(g)在PET基板上弯曲的TFT阵列光学影像

由于采用了独特的3D电流流动模式,高性能的电晶体得以消耗更低能量且更有效地作业。而且,相较于传统制造制程,由于研究人员的方法使其能够蚀刻更窄的沟槽,让他们也能在矽奈米薄膜(由于塑料基板上暴露的光衍射以及基板的热塑性,使其非常难以处理)上实现,此外,还可让半导体制造商在软性薄片上封装更多电晶体,以卷对卷(roll-to-roll )制程重复使用模具,从而大量制造软性电子。

根据研究人员表示,利用半导体奈米薄膜在塑料基板上所制造的软性电晶体,最小通道长度约为1um,这比他们提出的设计还大了10倍。