FIFO芯片IDT72V3680的功能特点及应用

于几乎满标志位,在WCLK的上升沿电平降低,而在RCLK的上升沿电平升高。在同步操作时,几乎空标志位只能随读时钟上升沿跳变,几乎满标志位只能随写时钟上升沿跳变。

(5)读写操作

读写操作可以通过异步读写引脚将读写操作设定为同步或异步方式。对于异步读写操作,芯片不能在FWFT模式下工作。

3 FIFO在高速数据传输系统中的应用

笔者所研究的高速数据传输系统是针对大容量的视频数据的压缩和解压缩性能研制的测试设备,在测试前后,需要将大容量的视频信号数据流从高档服务器中通过PCI接口读出或写入,系统所要求达到的指标是数据传输速率为62.5M字节/秒。PCI总线是高速端口,采用PCI总线进行数据传输,还应考虑到它与另一子系统间的数据传输协调及同步问题。如果这一子系统速率较低,整个系统的速率也将降低,PCI总线的优势将不能发挥出来。而采用FIFO存储器则不同,它不但提供了存储空间作为数据的缓冲,而且还可以在两个子系统之间提供一个“橡皮绷带式”(有弹性)的存储器,以使其在两端速率不一致的情况下,仍然可以实现两个子系统间的高速数据传输,而不需要解决相互同步和协调问题。IDT72V3680的工作时钟最高可达166MHz。

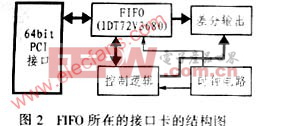

图2是FIFO所在的接口卡的结构框图。在这个设计中,PCI总线接口卡用来进行视频信号的高速传输和接收。双口存储器FIFO则作为PCI总线主控和后续或前端数据处理电路(如分路器、压缩、解压缩等电路)之间的数据通道。由于PCI总线经过PCI控制器转换后的插卡总线仍为同步总线,所以使用同步器件最能发挥总线的传输效率。在设计中,要求系统输出是8~12位长度的字节输出,而PCI总线的数据线输出位数是32位,由于该种FIFO有灵活的字节宽度匹配设置,因而免去了在逻辑设计中加入字节转换器的设计,这样不仅简化了控制逻辑设计的复杂度,而且提高了系统的速度及稳定性。该接口卡中的控制逻辑部分负责完成PCI9656的插卡总线和双口存储器之间的通信协议以及对前端或后端数据处理的传输控制。图3是IDT72V3680单芯片配置信号框图。

对FIFO芯片的时间运行模式、可编程标志位的时间模式、输入/输出字节宽度、缺省偏置值的选择等均可由拨动开关来设置;各标志位信号输出到控制逻辑可与前后端部分进行消息传递;读写时钟则由时钟产生电路提供。

4 结论

应用FIFO存储芯片可用其内部读写指针代替复杂的地址发生器,从而从硬件上简化了数据高速交换中与地址线相关的处理逻辑电路。高速FIFO存储芯片在PCI总线插卡设计中的应用能够保证高速系统数据传输的速度与效率。目前,FIFO芯片在众多的数据传输处理领域已得到广泛的应用。另外,由于FIFO存储芯片是成系列生产且功能相同,因此,随着存储容量的增加,外部引脚数不会增加,从而为以后系统的升级带来了方便。

特点 应用 功能 IDT72V3680 芯片 FIFO 相关文章:

- Linux 不仅仅是开源(04-04)

- DSP结构特点和运算性能(07-19)

- 现场总线的特点与优点(12-19)

- 现场总线控制系统的特点和优点(12-19)

- CAN总线学习系列之— CAN总线特点介绍(12-14)

- STM32中断式发送特点和RS485方向控制(12-02)