FIFO芯片IDT72V3680的功能特点及应用

FIFO芯片是一种具有存储功能的高速逻辑芯片,可在高速数字系统中用作数据缓存。FIFO通常利用双口RAM和读写地址产生模块来实现其功能。FIFO的接口信号包括异步写时钟(wr-clk)和读时钟(rd-clk)、与写时钟同步的写有效(wren)和写数据(wr-data)、与读时钟同步的读有效(rden)和读数据(rd-data)。写地址产生模块一般还根据读地址和写地址来产生FIFO的满标志。读地址产生模块一般根据读地址和写地址的差来产生FIFO的空标志。

为了实现正确的读写和避免FIFO的上溢或下溢,通常还应给出与读时钟和写时钟同步的FIFO的空标志(empty)和满标志(full),以禁止读写操作。写地址产生模块通常根据写时钟和写有效信号来产生递增的写地址,而读地址产生模块则根据读时钟和读有效信号来产生递增的读地址。

FIFO一般在操作时,首先在写时钟wr clk的上升沿且当wren有效时,将wrdata写入双口RAM中写地址对应的位置中,然后将读地址对应的双口RAM中的数据输出到读数据总线上,这样就可实现先进先出功能。读写操作一般会自动访问存储器中连续的存储单元。从FIFO中读出的数据顺序与写入的顺序相同,而地址的顺序则在内部已经预先定义好,因此,对FIFO芯片的操作不需要额外的地址信息。另外,FIFO芯片还能提供对读/写指针的复位功能。 2 IDT72V3680简介

2.1 IDT72V3680功能特点

IDT72V3680属于IDT公司的高密度supersyncTMⅡ36位系列存储器IDT72V3640~3690中的一种,其存储结构为16,384×36。这一系列CMOS工艺的FIFO(先入先出)芯片具有极大的深度。其基本功能特点如下:

- 对读/写口都可进行灵活的总线宽度设置,可选择不同的输入/输出数据线宽度(可在36 in 36 out;36 in 18 out;36in 9 out;18 in 36 out;9in 36 out中选择);

- 重传操作延时很低且固定;

- 首字的写入到读出的延时很低且固定;

- 数据密度高达1Mbit;

- 操作时钟可达166MHz;

- 可选大/小字节排列格式;

- 主复位方式可提供FIFO整体清零,部分复位只清掉存储数据,但保留可编程设置项;

- 几乎空/满标志置位或无效操作可选择同步或异步时间模式;

- 具有两种时间工作模式,分别为IDT标准模式(采用

和

和 标志位)和FWFT首字直传模式(采用

标志位)和FWFT首字直传模式(采用 标志位);

标志位); - 读写操作采用独立时钟,并可异步操作;

- 采用TQFP(128引脚)和PBGA(144引脚)两种封装形式,其中PBGA封装形式不仅可用JTAG口提供边界扫描功能,还可选择同步或者异步读写操作(只对PBGA封装);

- 与5V输入兼容;

- 具有节电模式;

- 管脚可与更高密度的芯片IDT72V36100和IDT72V36110兼容。

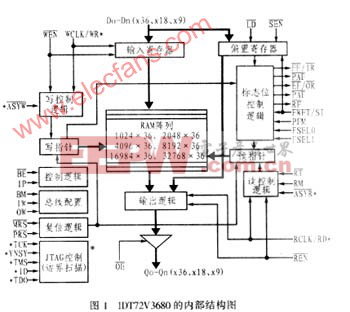

IDT72V3680的内部结构框图如图1所示。

2.2 使用要点

IDT72V3680系列产品在使用中,通常应注意以下几点:

(1)两种可选择的时间运行模式的区别

在主复位时,FWFT/SI信号电平为低表示选择IDT标准模式,否则表示选择首位字直传模式FWFT。在两种不同模式下,其输出的标志信号也有所不同,其中![]() 、

、![]() 为IDT标准模式;

为IDT标准模式;![]() (输出准备好)

(输出准备好)![]() 输入准备好)为FWFT模式。另一个区别是在FWFT方式下,第一个写入字在三个读时钟上升沿后将直接传到输出Qn上,而不需要

输入准备好)为FWFT模式。另一个区别是在FWFT方式下,第一个写入字在三个读时钟上升沿后将直接传到输出Qn上,而不需要![]() 信号有效,以后写入的字则需要

信号有效,以后写入的字则需要![]() 信号有效才能通过Qn传出;而在IDT方式下,写入字都需要

信号有效才能通过Qn传出;而在IDT方式下,写入字都需要![]() 有效才能读出数据。另外,FWFT在深度扩展时,FIFO可串行连接,即上一个FIFO的Qn直接连接下一个FI-FO的Dn,而无需额外控制逻辑。

有效才能读出数据。另外,FWFT在深度扩展时,FIFO可串行连接,即上一个FIFO的Qn直接连接下一个FI-FO的Dn,而无需额外控制逻辑。

(2)两种复位操作

IDT72V3680有主复位(MRS)和部分复位(PRS)两种方式(都属于异步操作)。当主复位启动后,读写指针都指向第一个数据位置,几乎空标志置低,几乎满标志和半满标志置高,同时,输入/输出的总线宽度、可编程标志位的同/异步方式以及是否需要去掉字节中的校验位均被确定,输出寄存器初始化为全零,上电即进行复位,以后才可进行写操作。而当部分复位后,只有读写指针复位,几乎空标志置低,几乎满标志和半满标志置高电平,其余各种运行方式不变,部分复位可在操作进行中进行复位,当经过编程设定的偏置值不理想时,可随时调用。

(3)加载操作

当![]() 置高时,可以采用串行的方式加载可编程标志位以生效偏置值;而当其置低时,则采用并行方式加载。读出这些偏置值时,只能采用并行方式。加载和读出偏置值的操作既可以被中断以执行普通数据的读写操作,也可以在主复位时通过FSL1、FSL0选择缺省的8种偏置值。

置高时,可以采用串行的方式加载可编程标志位以生效偏置值;而当其置低时,则采用并行方式加载。读出这些偏置值时,只能采用并行方式。加载和读出偏置值的操作既可以被中断以执行普通数据的读写操作,也可以在主复位时通过FSL1、FSL0选择缺省的8种偏置值。

(4)PAE、![]()

几乎空/满标志可由PFM引脚输入并将其设定为同步或异步模式操作。在异步操作时,几乎空标高速大深度新型FIFO存储器IDT72V3680的应用志位电平在RCLK的上升沿降低,而在WCLK的上升沿电平升高;对

特点 应用 功能 IDT72V3680 芯片 FIFO 相关文章:

- Linux 不仅仅是开源(04-04)

- DSP结构特点和运算性能(07-19)

- 现场总线的特点与优点(12-19)

- 现场总线控制系统的特点和优点(12-19)

- CAN总线学习系列之— CAN总线特点介绍(12-14)

- STM32中断式发送特点和RS485方向控制(12-02)